The following are trademarks of Altera Corporation: A+PLUS, LogicMap, LogiCaps, MacroMuncher, TURBO-BIT, SALSA, ADLIB, SAM+PLUS, PLDS-SAM, PLS-SAM, SAM+PLUS, SAMSIM, ASMILE, PLDS2, PLS4, PLS2, PLCAD, PLE, ASAP, EP300, EP310, EP320, EP512, EP600, EP610, EP630, EP900, EP910, EP1200, EP1210, EP1800, EP1810, EPS448, EPB1400, EPB2001, EPB2002, EPM5016, EPM5024, EPM5032, EPM5064, EPM5127, EPM5128, EPM5130, EPM5192, SAM, BUSTER, MCMAP, MAX, and MAX+PLUS. A+PLUS and MAX+PLUS design elements and mnemonics are Altera Corporation copyright. IBM is a registered trademark of International Business Machines, Inc. PS/2 and Micro Channel are trademarks of International Business Machines, Inc. CHMOS is a trademark of Intel Corporation. PC-CAPS is a trademark of Personal CAD Systems Inc. DASH is a trademark of FutureNet Corporation. PAL and PALASM are registered trademarks of AMD/MMI. MS-DOS is a trademark of Microsoft Corporation. Altera reserves the right to make changes in the devices or the device specifications identified in this document without notice. Altera advises its customers to obtain the latest version of device specifications to verify, before placing orders, that the information being relied upon by the customer is current. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty. Testing and other quality control techniques are used to the extent Altera deems such testing necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed. In the absence of written agreement to the contrary, Altera assumes no liability for Altera applications assistance, customers product design, or infringement of patents or copyrights of third parties by or arising from use of semiconductor devices described herein. Nor does Altera warrant or represent that any patent right, copyright, or other intellectual property right of Altera covering or relating to any combination, machine, or process in which such semiconductor devices might be or are used.

Altera's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of Altera Corporation. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonable expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

ALTERA cannot assume any responsibility for any circuits shown or represented that they are free from patent infringement.

Products contained within are covered by one or more of the following U.S. patents: #4,609,986; #4,677,318; #4,617,479; #4,713,792; #4,328,565; #4,361,847; #4,409,723; #4,639,893; #4,649,520; and the following foreign patents: England: #2,072,384; #2,073,487; West Germany: #3,103,160; and Japan: #1,279,100. Additional patents pending.

Copyright © 1990

ALTERA Corporation

Altera Corporation 2610 Orchard Parkway San Jose, CA 95134-2020 (408) 984-2800 Applications Information: (408) 984-2805 ext. 102

### **About This Handbook**

This handbook contains a collection of product information bulletins, datasheets, application notes and briefs, and various other pieces of information about Altera's MAX devices and development tools.

- Section 1 includes an overview of the MAX architecture and a discussion of the technology issues and alternatives in the application-specific market. This section also answers some questions asked from a manager's perspective.

- Section 2 describes the entire MAX EPLD family, MAX+PLUS software, and optional products, and provides recommendations for designing with MAX devices.

- Section 3 addresses specific applications for MAX devices and MAX+PLUS software.

- Section 4 provides instructions on how to use Altera's Electronic Bulletin Board and how to order MAX products. It also includes a list of currently available Applications literature.

If this handbook doesn't answer your technical questions, please call Altera Applications at (408) 984-2805 ext. 102 for immediate assistance.

## **Contents**

|           | About This Handbookiv                                 |

|-----------|-------------------------------------------------------|

|           | Contentsv                                             |

|           | MAX—The Industry-Standard Programmable Logic Familyvi |

| Section 1 | MAX Family Overview                                   |

|           | MAX EPLD Family Architecture                          |

| Section 2 | Data Sheets                                           |

|           | MAX Family: Device & Software Overview                |

| Section 3 | Application Notes and Briefs                          |

|           | Integrating PAL and PLA Devices with the EPM5032      |

| Section 4 | General Information                                   |

|           | Electronic Bulletin Board Service                     |

2

3

4

# The Complete Industry-Standard Programmable Logic Family

- ☐ The Altera EPM-series of Multiple Array MatriX (MAX) EPLDs offers the industry's most comprehensive family of programmable logic building blocks.

- ☐ Advanced MAX architecture provides the speed, ease of use, and familiarity of PAL devices with the density of programmable gate arrays.

- ☐ Modular family structure solves design tasks from fast 20-pin address decoders to 100-pin LSI custom peripherals.

- ☐ Non-volatile, reprogrammable EPROM technology aids prototype development.

- ☐ High sequential logic capacity provides up to 384 registers plus latches.

- ☐ Up to 66 product terms per output ensure efficient design of complex state-machines.

- ☐ Exactly emulates all popular 7400-series functions to convert existing CMOS and TTL designs.

- ☐ Easily integrates multiple-package PAL and PLA designs.

- ☐ Provides 15-ns combinatorial delays, counters up to 100 MHz, pipelined data rates of 100 MHz, and high-complexity designs with true system clock rates up to 66 MHz.

- ☐ A full selection of packages is provided, including DIP, SO, J-lead, PGA, and QFP formats in windowed ceramic and plastic OTP versions.

- ☐ Easily converts to custom-masked silicon for very high-volume production.

- MAX+PLUS PC-based design tools including hierarchical schematic and advanced hardware design language entry methods, efficient logic synthesis-based compiler, and full timing simulation support MAX EPLDs.

- ☐ Logic compilation and automatic place and route of 1000+ gate designs performed in minutes.

- ☐ EDIF industry-standard workstation and third-party CAE tool interfaces are available.

## **Contents**

| About This Handbookiv                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| MAX Family Overview                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| MAX EPLD Family Architecture                                                                                                                                                                                                                                                                         | 1<br>9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| Data Sheets                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| EPM5016 to EPM5032: MAX EPLDs with a Single LAB                                                                                                                                                                                                                                                      | 33<br>83<br>85<br>97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

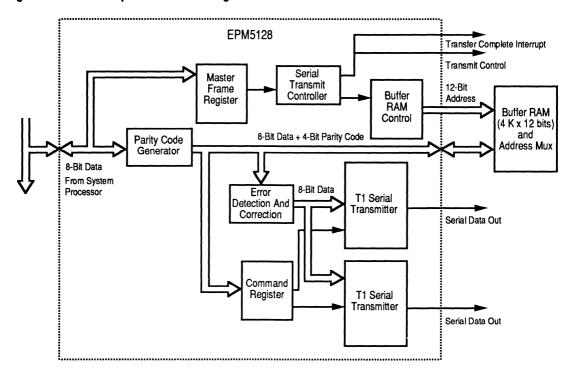

| Integrating an Intelligent I/O Subsystem with a Single EPM5128 Understanding MAX EPLD Timing Using Expanders to Build Registered Logic in MAX EPLDs Design Guidelines for MAX EPLDs Optimizing Memory for MAX+PLUS Simulating Internal Nodes Choosing the Right EPLD for a State Machine Application | 123<br>141<br>153<br>159<br>167<br>173<br>183                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| General Information  Electronic Bulletin Board Service Ordering Information Package Outlines Applications Literature                                                                                                                                                                                 | 197<br>199<br>201<br>202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                                                                                                                                                                                                                                                                      | MAX Family Overview  MAX Family Architecture MAX—A Manager's Perspective  Data Sheets  MAX Family: Device & Software Overview EPM5016 to EPM5032: MAX EPLDs with a Single LAB EPM5064 to EPM5192: MAX EPLDs with Multiple LABs Design Recommendations for MAX EPLDs PLDS-MAX/PLS MAX: MAX+PLUS Programmable Logic Development System PLDS-ENCORE: Programmable Logic Development System MAX+PLUS PLSA Tools for Logic Synthesis Analysis PLDVS: General Purpose PC-Based Tester  Application Notes and Briefs Integrating an Intelligent I/0 Subsystem with a Single EPM5128 Understanding MAX EPLD Timing Using Expanders to Build Registered Logic in MAX EPLDs Design Guidelines for MAX EPLDs Optimizing Memory for MAX+PLUS Simulating Internal Nodes Choosing the Right EPLD for a State Machine Application Troubleshooting Programming Problems |  |  |  |

### MAX EPLD

### **Family Architecture**

January 1990

**Product Information Bulletin 4**

### Introduction

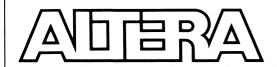

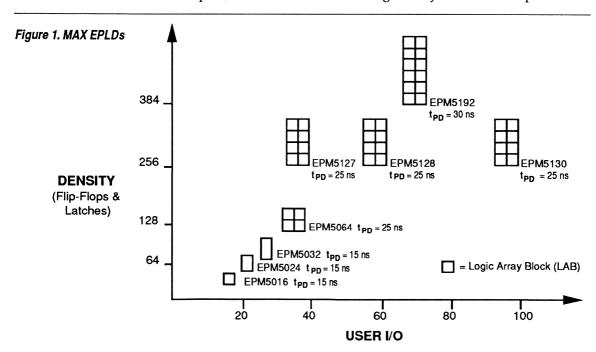

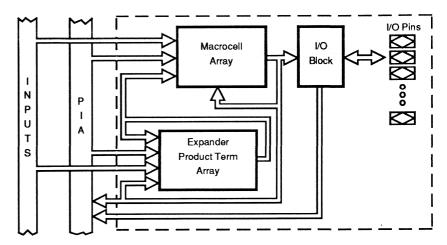

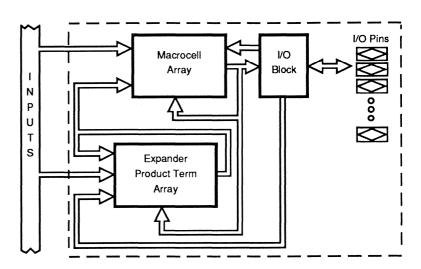

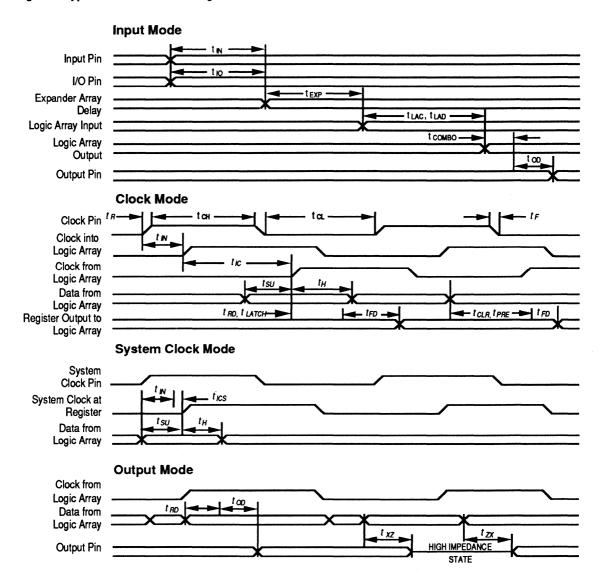

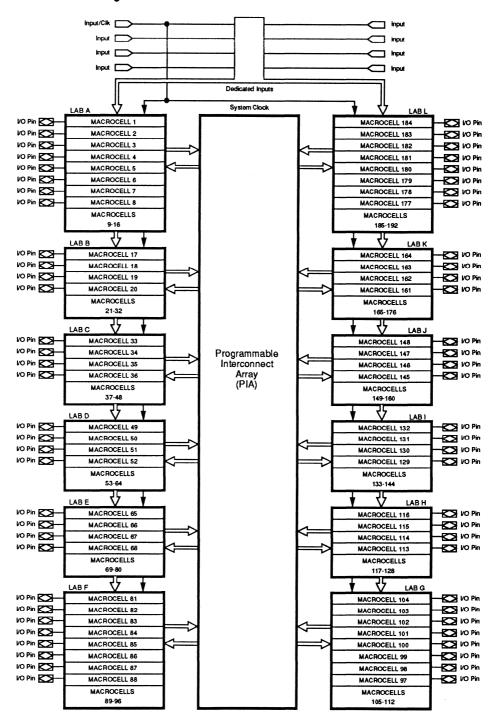

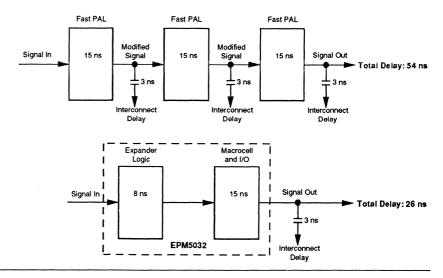

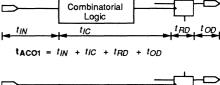

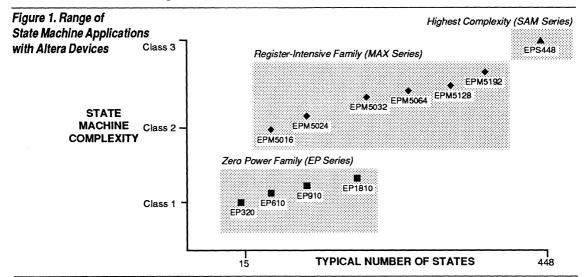

MAX (Multiple Array MatriX) Erasable Programmable Logic Device (EPLD) architecture was developed to provide the foundation for the first complete high-performance CMOS logic family based on user-configurable technology. Earlier PLDs have found efficient application in selected replacement of standard TTL and CMOS logic products. However, inconsistency of architecture between devices, limitations in logic features, and low device densities have prevented their wide acceptance as a primary logic solution. The MAX EPLD approach breaks through these barriers. See Figure 1.

MAX architecture has evolved from the original EPLD structure, achieving both higher performance and more efficient use of logic resources. The powerful logic array structure and the familiar and easy use of PAL devices and EPLDs are retained as well as the logic density of gate arrays. Additional MAX architecture enhancements permit the integration of high-density combinatorial and register-intensive logic functions. The result is a flexible family of EPLDs that accommodates exact functional equivalents of hundreds of popular 7400-series elements.

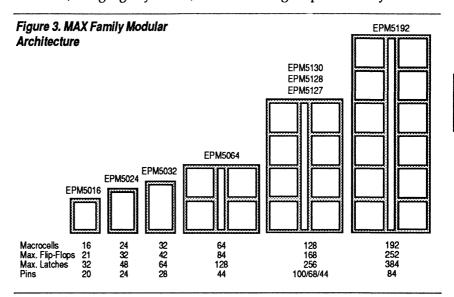

Figure 1. MAX Family Modular Architecture

These features are incorporated into the EPM5000 series of EPLDs from Altera. They comprise a consistent series of modular logic building blocks ranging from 20-pin dual-in-line packages to 100-pin pin-grid array and surface-mount packages. The integration density of these devices ranges from 2 or more PAL devices at the low end to 24 to 30 devices at the upper end. The latter range is equivalent to 100 or more standard TTL packages.

The most important objective for the MAX architecture was to overcome the serious limitations of earlier PLD structures, which were unable to achieve higher levels of integration of TTL-based designs. These limitations traditionally have included fixed product-term distribution, lack of register control inputs, and tight coupling of register and I/O pin resources, to name a few. The following pages review the key features of the MAX architecture and describe how MAX EPLDs overcome these deficiencies. Additional technical information is provided in references listed at the end of this Product Information Bulletin. The reader should be familiar with the general characteristics and terminology of PLD technology.

### Basic MAX Architecture

Small array performance, large array density.

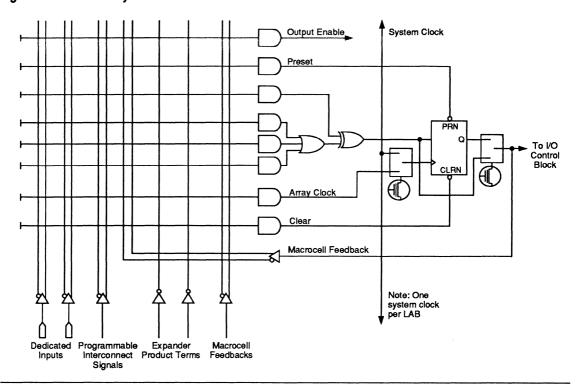

At the top level, the MAX approach is based on the concept of a small, high-performance, flexible logic array module called a Logic Array Block (LAB).

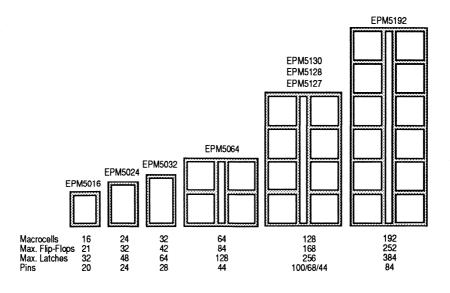

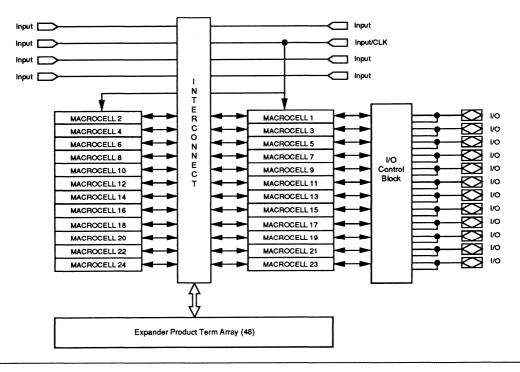

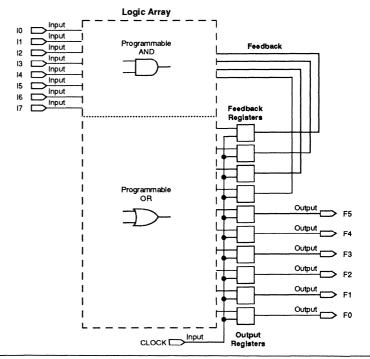

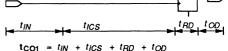

Smaller members of the MAX family (EPM5016, EPM5024, and EPM5032) have a single LAB. In these devices, all logic signal sources and destinations are fully interconnected directly on the device within the LAB, as shown in Figure 2.

Figure 2. LAB Block Diagram

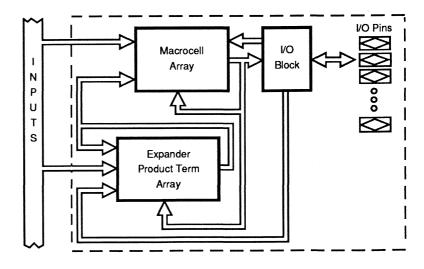

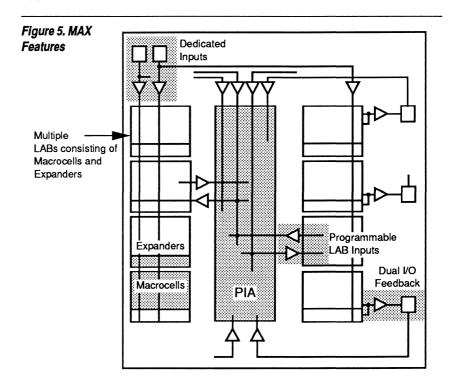

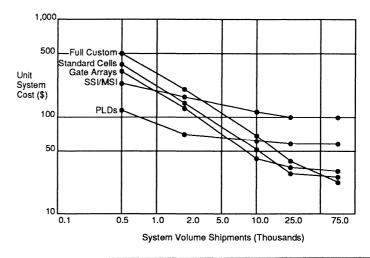

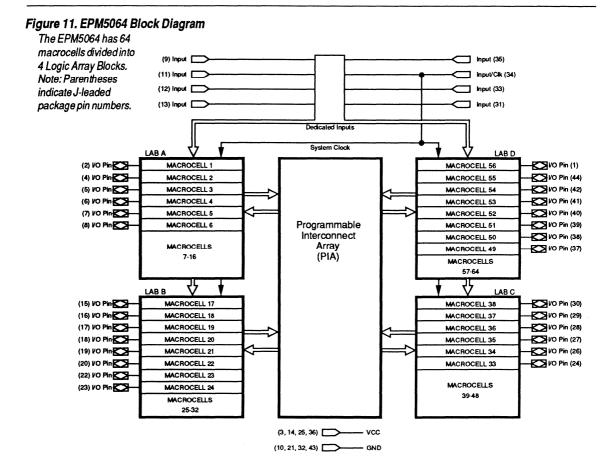

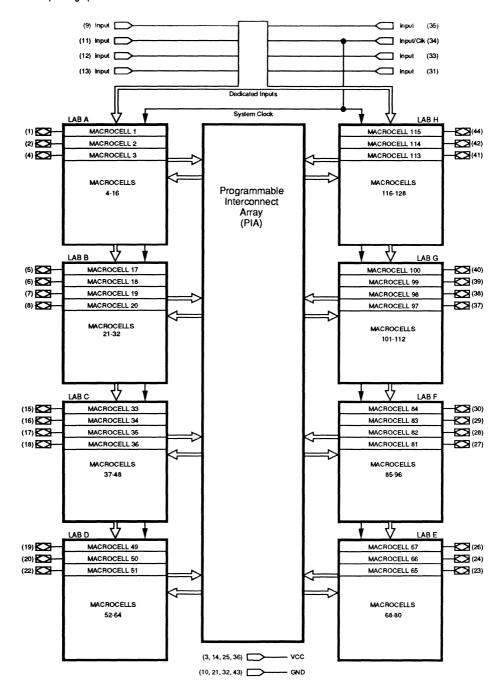

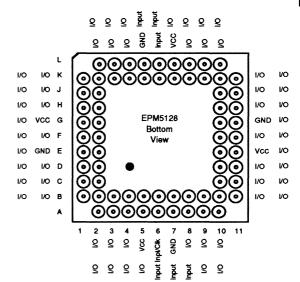

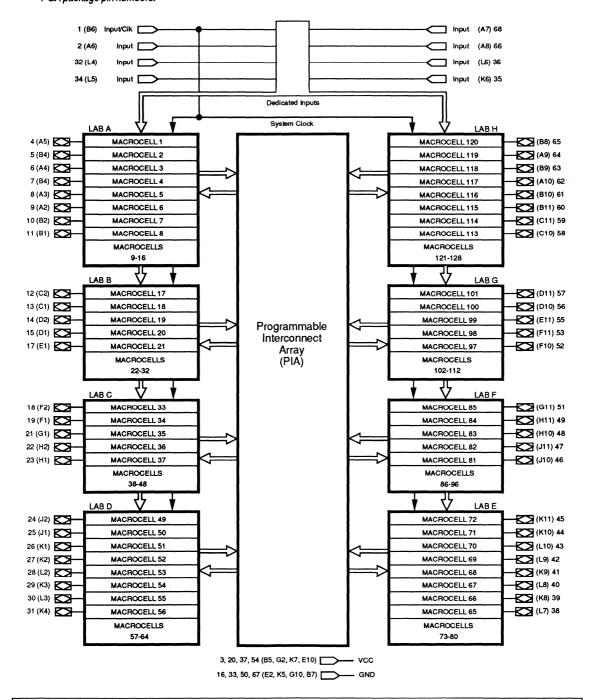

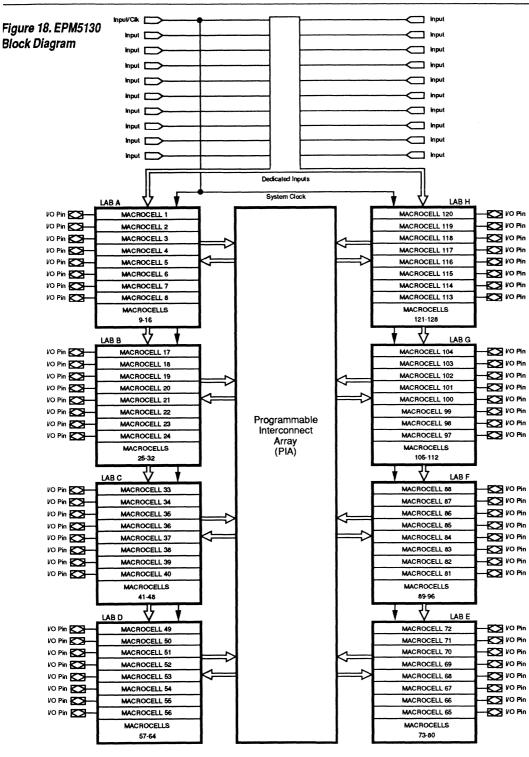

In larger MAX devices (EPM5064, EPM5128, EPM5130, EPM5192), multiple LABs are linked together via a dedicated, programmable interconnect network called a Programmable Interconnect Array (PIA). The PIA permits any signal source to reach any destination on the chip without routing constraints. This structure allows interconnection of many LABs, achieving large array density with the high performance of small arrays.

The PIA, shown in Figure 3, acts as a programmable highway between all logic functions on the chip. Unlike masked or programmable gate arrays with routing "channels," the PIA provides a crosspoint switch for logic communication, eliminating possible routing bottleneck problems. It also yields a predictable uniform delay. Only a single, fixed-array delay is incurred in the interconnection. Moreover, the delay is substantially smaller than the macrocell delay. The variable and cumulative delays of gate arrays are eliminated.

Figure 3. Key MAX Features

The ability to interconnect all points ensures rapid, automatic design completion on low-cost, accessible, PC-based workstations. Typical MAX designs can be routed in minutes. In contrast, high-density, programmable gate array designs can take hours or days, and in many cases require significant manual intervention. Furthermore, incremental, additive delays between various points can cause debilitating skew and glitch problems, which require additional—often multiple—iterations of the design.

# The MAX Macrocell

PLA flexibility with PAL economy and performance.

Formerly, PLDs have been classified as either PLA (programmable-AND/programmable-OR) or PAL (Programmable-AND/fixed-OR) devices. The former offers greater logic flexibility, whereas the latter has faster input/output delays and is easier to use. However, in some applications, the PAL structure can be inefficient due to fixed allocation of product terms (p-terms) per output. Typically, 70% of designs require 3 or fewer p-terms. To accommodate as many as possible of the remaining 30%, existing PAL devices and EPLDs use groups of 8 or more p-terms. Thus, at least 5 p-terms are wasted most of the time.

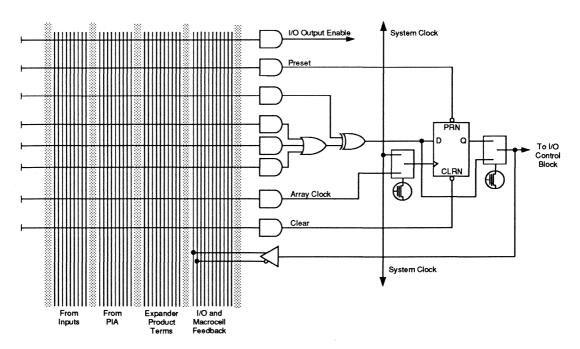

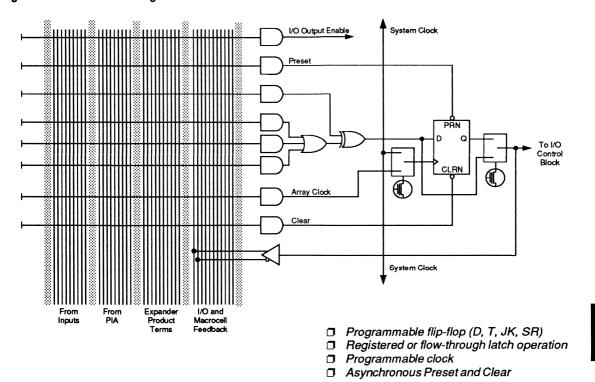

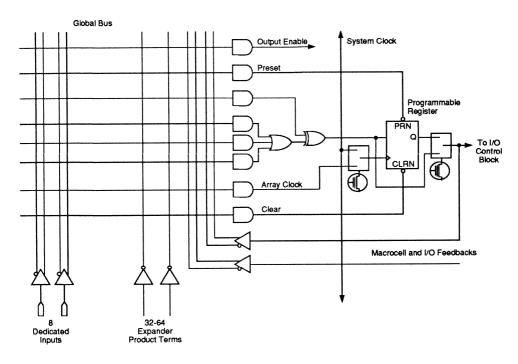

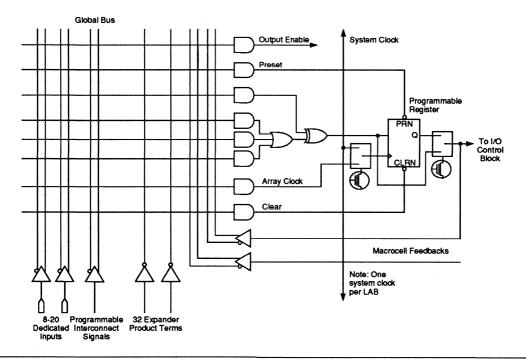

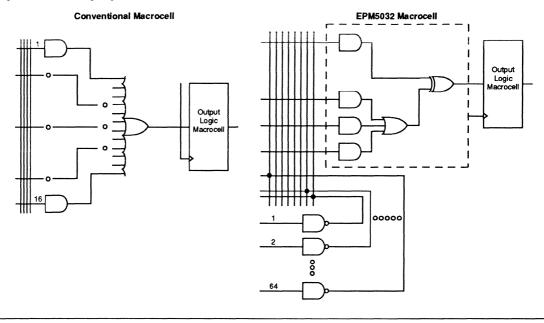

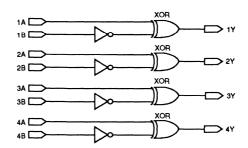

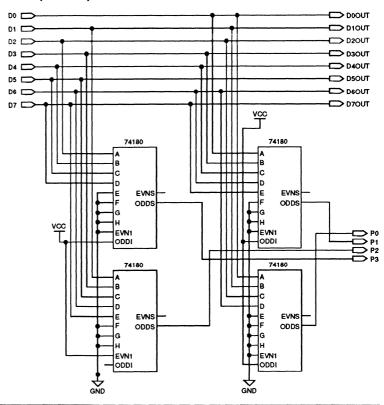

Inside the MAX Logic Array Block are groups of p-terms feeding a sequential logic element. These groups are called macrocells. Each LAB contains between 16 and 32 macrocells. The macrocell in MAX has been designed to combine the flexibility of the PLA device with the speed of the PAL device while eliminating the silicon inefficiency of the latter. Three fixed p-terms are assigned to each MAX macrocell. These are ORed together to drive one input of an XOR (exclusive-OR) gate. The other input of the XOR gate is driven by another product term from the logic array. See Figure 4.

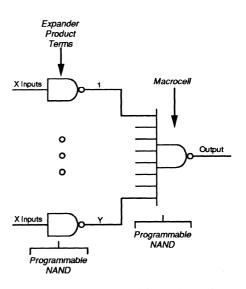

When a logic function requires more than the three fixed p-terms, additional p-terms may be allocated to any macrocell from a pool of uncommitted single p-terms, called Logic Expanders, contained within the LAB.

Figure 4. Macrocell Block Diagram

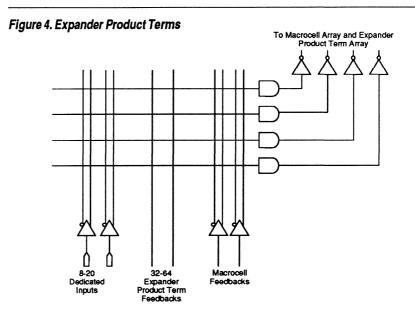

### Logic Expanders

Logic where it is needed.

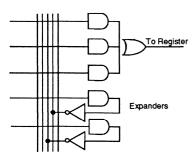

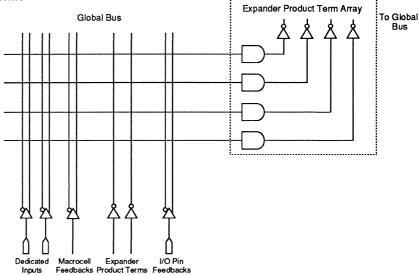

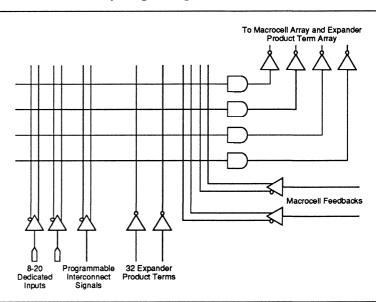

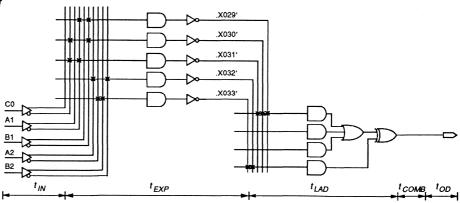

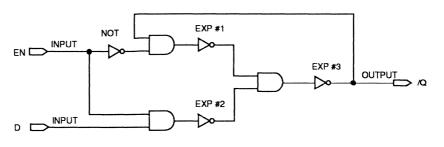

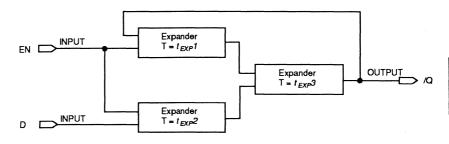

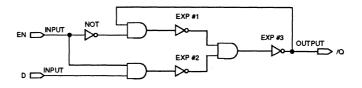

Figure 5. Logic Expanders

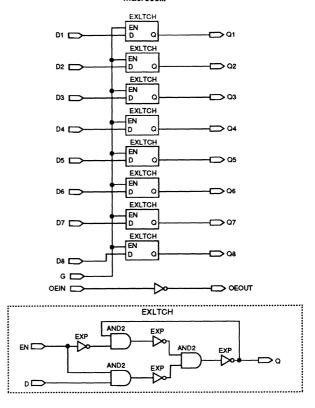

Expanders may be viewed as single product terms with inverted outputs feeding back into the LAB. Expanders provide the PLA-like flexibility of the MAX macrocell. See Figure 5.

Inputs available to the expanders are the same as those for the macrocells in the LAB. Expanders may be distributed to those macrocells that require more than 3 p-terms to implement a desired logic function. The number of fixed p-terms and expanders provided in each LAB has been statistically

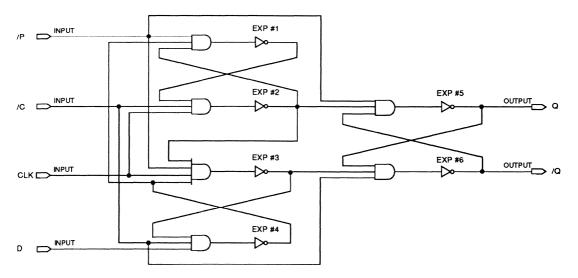

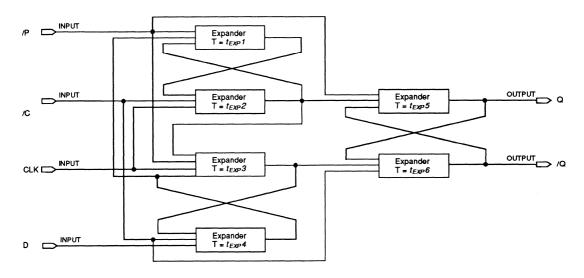

determined by analyzing hundreds of typical 7400-series TTL and CMOS logic designs as well as PLD-based system designs. Up to 32 expanders are available in an LAB, i.e., all 32 p-terms may be allocated to a single macrocell, or they may be spread among all macrocells. Since expander outputs are available to all macrocells in the LAB, common logic functions may be generated once and used by multiple macrocells. Most importantly, expander logic propagation delays are substantially shorter than macrocell delays for best performance.

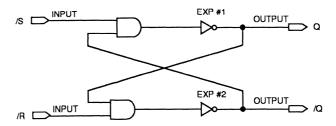

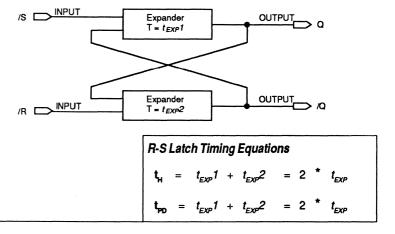

The expander array can be viewed as a "sea of AND gates" that may be used for sequential and combinatorial functions. Since expanders have inverting outputs, they may be cross-coupled to generate an RS-latched element. Six expanders can be used to create buried, edge-triggered D-type flip-flops, effectively increasing the register

count by 33%. When asynchronous latches can be used, this capability can double the total available storage capacity of a MAX device.

This buried flip-flop feature is extremely useful for complex state machine designs. It may be used to hold internal state variables, saving the fixed macrocell flip-flops for decoding of states to the output pins.

## Multi-Mode Macrocell Flip-Flop

Latch, D-, JK-, RS-, or T-type.

The basic sequential element in the macrocell may be programmed to operate in either a flow-through latch or edge-triggered (D-type flip-flop) register mode. Flow-through latching provides minimum input-to-output delays for speed-critical applications such as chip select decoding. Edge-triggered operation guarantees glitch-free output generation for applications such as synchronous counters or state machines. A combinatorial output function is realized by bypassing the register.

The output of an XOR gate drives the input to the macrocell's D-type flip-flop. This XOR allows selective inversion of the logic function for polarity control or logic minimization, in addition to direct generation of parity trees, adders, etc. It may be also be used in association with the D-type flip-flop element to emulate JK-, RS-, or T-type functions.

The dedicated sequential elements in the macrocells combined with those obtainable from the expanders give the MAX architecture three to four times more storage capacity than a conventional PAL structure in the same size package.

# Flexible Macrocell Control

True emulation of TTL functions.

Each macrocell provides individual asynchronous Preset and Clear, allowing for implementation of asynchronous load counters and true emulation of all popular 7400-series TTL sequential functions. Earlier PLDs and programmable gate arrays do not offer this feature, and designs have to be reworked to fit the devices' more rigid architectures.

Flip-flops can be configured for synchronous or asynchronous clocking. Synchronous clocking provides a direct connection from a dedicated clock pin minimizing clock-to-output delays. Asynchronous clocking provides the flexibility to clock flip-flops individually from logic. The logic expander array may be used to generate multiple p-term controls for the Clock, Output Enable, Preset, and Clear functions. In contrast, most PLDs have only a single control that consumes an additional macrocell to create relatively simple gated logic functions.

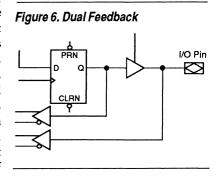

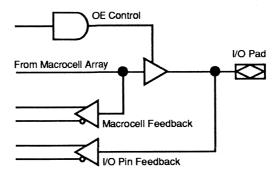

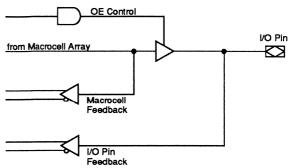

## Dual Feedback on All I/Os

All registers can be buried.

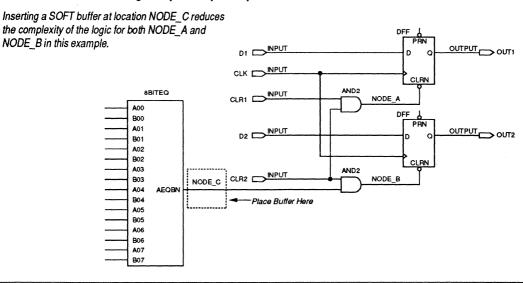

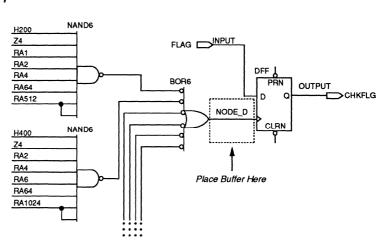

In most PLD architectures, when an I/O pin is used as an input, the macrocell associated with that pin cannot be used and is wasted. In the

MAX architecture, the I/O pins and macrocell resources (e.g., registers) are decoupled. By providing independent I/O pin and macrocell feedback paths into the array, as shown in Figure 6, all registers can potentially be buried, while I/O pins are used as general inputs to device logic. For example, the EPM5128 may be configured as an 8 input/52 output function or as a 59 input/1 output function without reducing the effective number of register bits available.

# Sub-Micron Technology

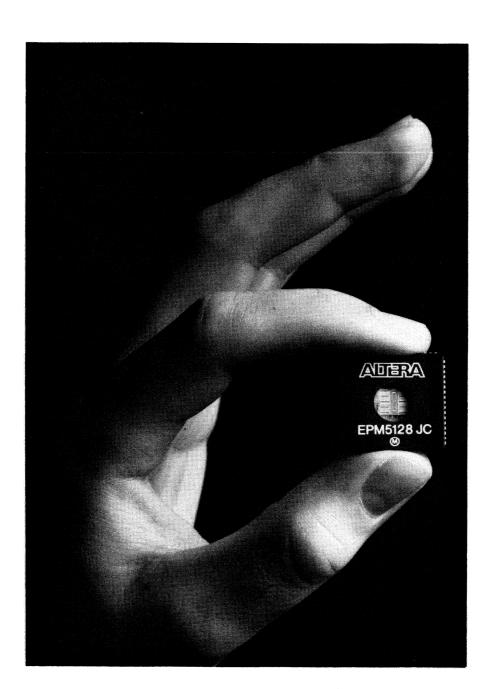

The MAX family is based on a 0.8-micron, double-metal CMOS EPROM technology. The first 8 members of the family, with macrocell counts from 16 to 192, will be available in packages with pin counts ranging from 20 to 100 leads, in DIP, chip carrier, quad flat pack (QFP), and PGA versions where appropriate. They will be available in both UV-erasable/reprogrammable ceramic devices as well as in economical one-time-programmable (OTP) plastic units.

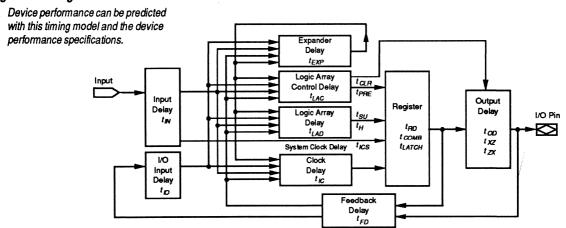

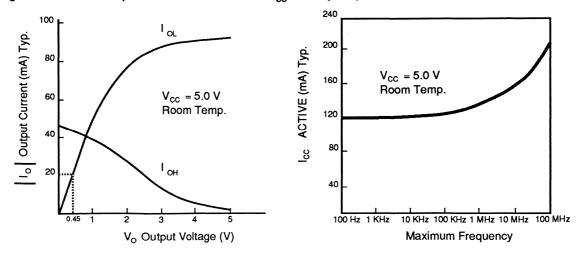

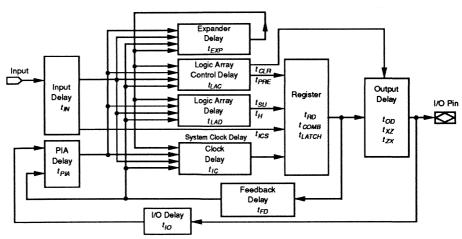

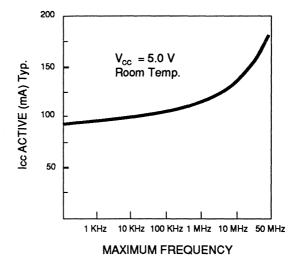

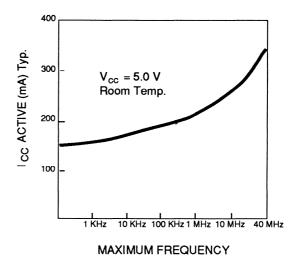

Performance characteristics of this technology are excellent. Internal operating frequencies are 40 to 100 MHz depending on device density. On the EPM5128, 30-ns delays from dedicated input to device output are obtainable, and 15-ns delays on the EPM5016. The EPM5016 also features flip-flop clock-to-output delays of 9 ns. Unlike other high-density PLD technologies (such as programmable gate arrays) that quote extreme f<sub>MAX</sub> numbers, which must be derated for a real application by two to ten times, MAX performance is realistic and predictable.

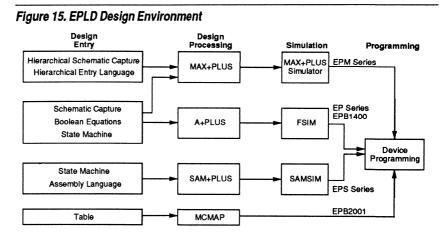

### MAX+PLUS

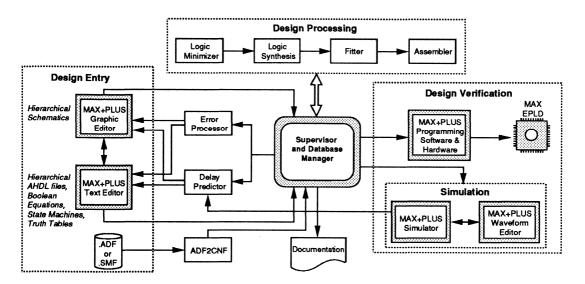

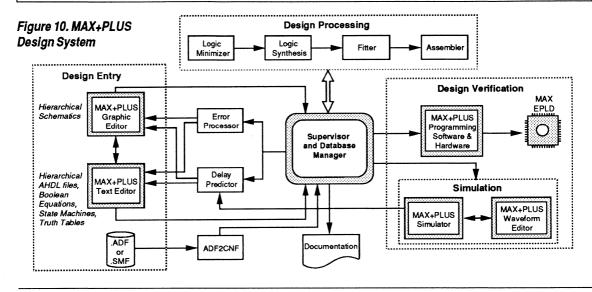

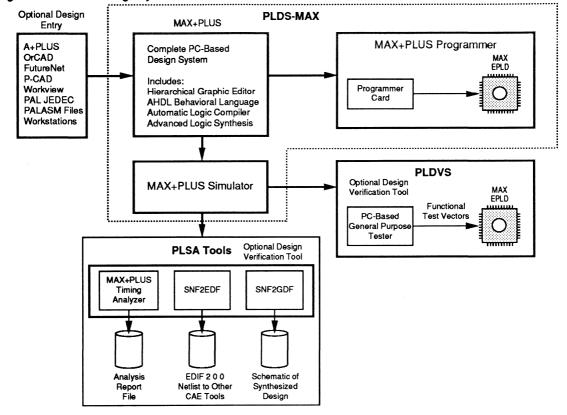

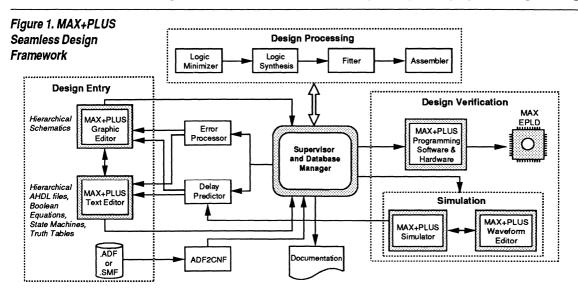

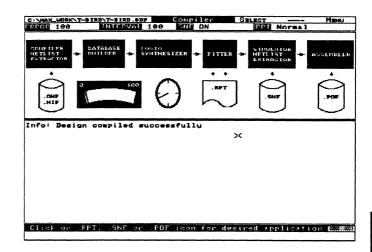

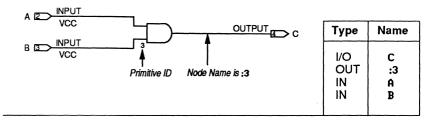

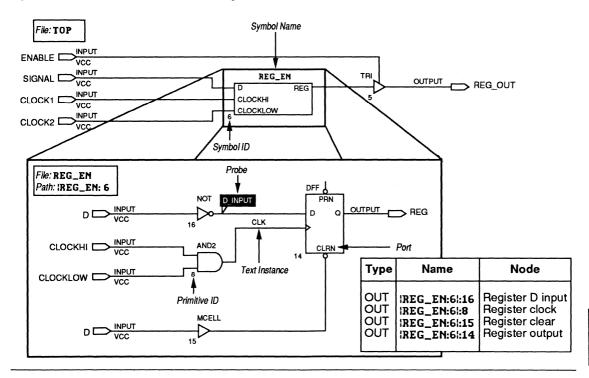

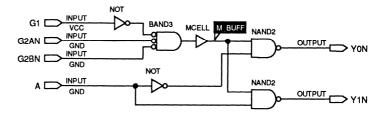

Harnessing the power of the MAX architecture is easy with the aid of Altera's sophisticated CAE tools. To support designs for MAX devices, Altera provides MAX+PLUS, a new generation of PC-based PLD design software. MAX+PLUS offers a comprehensive front-to-back design system for the entire MAX family. Hierarchical design entry, automatic logic minimization, device fitting (analogous to automatic place-and-route), timing simulation, and programming support are provided. See Figure 7.

Figure 7. MAX+PLUS

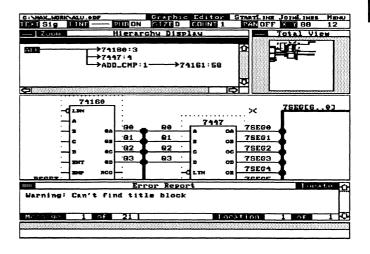

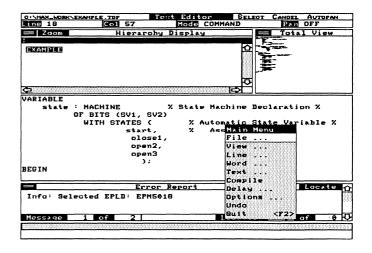

The MAX+PLUS user interface is graphics-based. TTL macrofunctions with SSI and MSI symbols provide a familiar design entry, while the Altera Hardware Description Language (AHDL) with optimized state-machine syntax provides powerful text design entry. Multiple menus offer access to various MAX design processing and simulation sub-systems. Errors discovered during design processing are reported and highlighted in the appropriate schematic or text file for easy debugging.

The MAX+PLUS Compiler uses sophisticated logic synthesis and minimization algorithms to get the most out of the silicon. Extraction of common logic factors to minimize expander consumption, recognition of primitive XOR functions, and multi-level logic compaction are a few of the techniques used. The user need not worry about "pre-packing" logic: the software provides the optimization.

Design fitting in MAX+PLUS is analogous to gate-array place-and-route. However, the PIA eliminates the worry that the software may run out of

routing channels. As a result, there are no functional restrictions on the connections between individual logic blocks. Once the design is fitted, the software generates a device programming file to specify the final design template for the target EPLD.

Timing simulation with graphic waveform output is integrated into MAX+PLUS. Real MAX performance can be predicted with 100-picosecond resolution. To evaluate a design, the MAX user can simulate it rapidly on the PC, or program a device and insert it into the breadboard.

This table summarizes the features of MAX-optimized PLD architecture:

| Feature                                                                 | Benefits                                                     |

|-------------------------------------------------------------------------|--------------------------------------------------------------|

| Multiple Array Matrix Architecture                                      | Large array density with fast, small array performance       |

|                                                                         | High logic fan-in (>80) and fan-out<br>(>128)                |

| Logic expanders                                                         | No wasted logic product terms (100% utilization is possible) |

|                                                                         | Additional sequential logic capacity                         |

| Programmable Interconnect Array                                         | Efficient on-chip routing with predictable delays            |

| Macrocell flip-flops                                                    | Programmable D,T, JK, SR types                               |

| Asynchronous Preset and Clear                                           | True emulation of 7400-series TTL                            |

| Multiple product term control of Clock,<br>Output Enable, Preset, Clear | Reduced macrocell consumption and reduced logic delays       |

| Dual I/O feedback                                                       | All registers and pins may be used independently             |

The EPM5000 series of MAX EPLDs is the first complete, high-performance CMOS logic family intended as a general-purpose, high-integration solution to a wide range of applications. Through exploiting the benefits of user-configurable technology, and through multiple source licensing agreements on both development tools and silicon production, Altera aims to establish MAX as the industry-standard logic family of the 1990s.

### References

Cole, Bernard C. "Altera Pushes EPLDs." *Electronics* (May 12, 1988). "Dreifache Komplexität und Doppelte Geschwindigkeit für EPLDs." *Design und Elektronik* (5. Juli 1988).

Faria, Don F. and Robert K. Beachler. "MAX EPLDs Provide Solutions to Both Gate Intensive and Register Intensive Applications." *Professional Program Session Record* 31, *Electro*/88 (May, 1988).

Halleux, Patrick de. "Densité triplée et performance doublée, pour les EPLD d'Altera." *Electronique Industrielle* No. 145 (January 6, 1988).

Lytle, Craig. "MAX+PLUS Eases High-Density EPLD Design Entry." Professional Program Session Record 14, Electro/88 (May, 1988).

"Multiple Array Matrix High Density EPLDs." Altera Advanced Information Data Sheet (1988).

# MAX A Manager's Perspective

January 1990

**Product Information Bulletin 5**

### Introduction

Today, more than ever, managing the development of a digital system is a challenge. From product specification to production transfer, the development strategy must emphasize performance, timeliness, and cost-effectiveness. A major factor in maintaining a product's competitiveness in the marketplace is the selection of state-of-the-art logic design technology—a technology that can satisfy the customer's logic integration needs and time-to-market requirements, as well as quickly accommodate changing system specifications and product features.

"...your development strategy must emphasize performance, timeliness and cost-effectiveness." Altera's new Multiple Array MatriX (MAX) family offers a combination of logic density, performance, and flexibility that's tough to beat. The EPM5000 MAX series of EPLDs comprises 8 devices with a range of densities to meet logic application needs at system clock rates up to 66 MHz and pipeline data rates of over 100 MHz. A MAX solution is available for every problem—be it a 20-pin device ideal for high-speed address decoding and state machines, or a a 100-lead device that accommodates several thousand gates. And every MAX family member has a fully programmable architecture that efficiently fits any mix of TTL functions without the design and routing headaches commonly associated with fixed and programmable gate arrays.

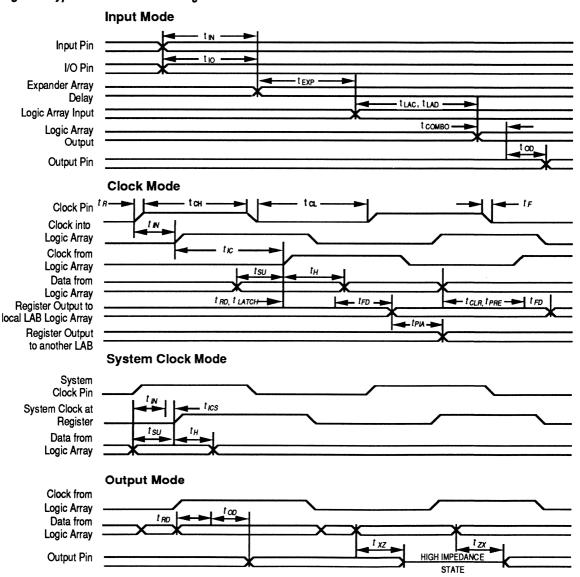

Design tools are the critical link between designer and chip. The advanced MAX+PLUS system supports multiple design entry methods, including familiar TTL schematic design entry, so a designer won't have to learn a whole new language. The MAX+PLUS Compiler uses logic synthesis that automatically translates a high-level design into a MAX programming file in minutes. So, a programmed EPLD can be in the system just moments after the design is completed.

This Product Information Bulletin addresses questions commonly asked by management about the MAX product family and Altera. The MAX architecture's technical features and benefits are summarized in *Product Information Bulletin 4 (MAX Family Architecture)*.

# Questions & Answers

#### ♦ Who is Altera?

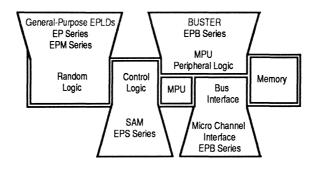

Over the past six years, Altera Corporation has pioneered the concept of large-scale, erasable, programmable logic devices—EPLDs. EPLDs and advanced PC-based design tools are Altera's only business (see Figure 1).

Figure 1. Altera User-Configurable Logic Families

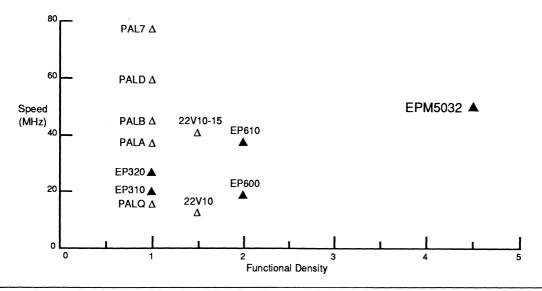

According to Dataquest, a market research group, Altera is the #1 supplier of large and small CMOS programmable logic devices in the world today (see Figure 2). General-purpose EPLDs effectively solve a wide range of logic design problems. Altera has extended the EPLD concept to special-

purpose programmable logic devices called function-specific EPLDs. These include the EPS-series of Stand-Alone Microsequencer (SAM) components

for high-performance control logic and the EPB2001 Micro Channel Interface device. These devices provide optimized logic functions to solve specific application problems.

To establish the EPLD concept as an industry standard, Altera Corporation, based in San Jose, California, has entered second-source relationships with Cypress Semiconductor, Intel Corporation, Texas Instruments, and Wafer Scale Integration (WSI).

Altera

Altera

CMOS PLD Suppliers

### Why will MAX replace TTL and CMOS logic families, as well as PLA and PAL devices and many ASICs?

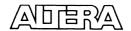

The MAX family (shown in Figure 3) will become the new standard logic design technology for the 1990s because it offers:

- ☐ User-Configurability—Design to silicon in minutes

- ☐ Performance—Real performance compatible with today's highperformance microprocessors

- ☐ Integration—Packing dozens of components into a single chip in through-hole and surface-mount packages

- ☐ I/O Options—Providing pin counts from 20 to more than 100 pins in convenient density increments

- ☐ Ease of Use —Familiar, programmable logic-array based architecture gives predictable in-system performance. MAX+PLUS PC-based design tools, using logic synthesis, maximize designer productivity.

### ♦ How efficient is MAX? How much logic can a designer put into a chip?

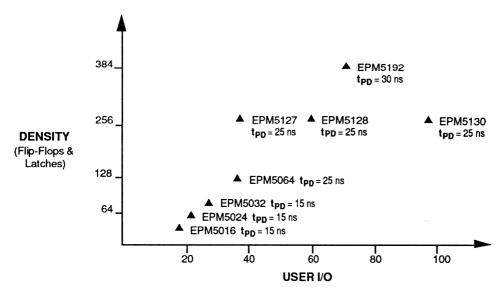

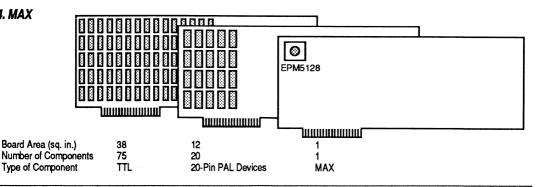

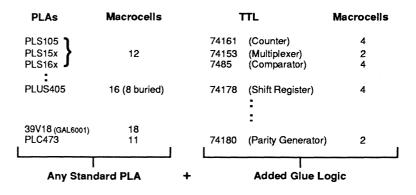

The MAX family offers a range of device densities. The 68-pin, J-lead EPM5128 can integrate the equivalent of 20 PAL devices or a typical mix of 75 MSI/SSI TTL chips into a single device; e.g., as many as 128 74151 multiplexers, or 32 four-bit 74161 counters can be designed into a single device. On the other end of the spectrum, the EPM5032 can integrate 4 to 6 PAL devices into a single 28-pin DIP package (equivalent to 10 to 15 TTL components). Other MAX family members offer density and I/O counts above and below these two limits. See also Figure 4.

Figure 4. MAX Board Density

Altera Corporation

Page 11

"...MAX's

Programmable

Interconnect Array (PIA)

provides 100%

routability."

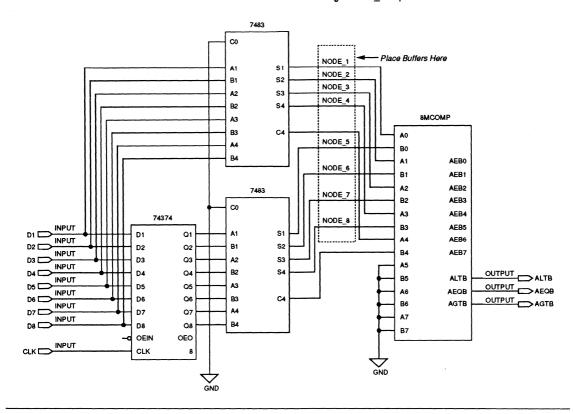

As Figure 5 shows, the MAX architecture is extremely efficient. Unlike programmable gate array technologies, which have severe logic interconnection (routing) limitations that stretch design time and reduce gate utilization dramatically, MAX's Programmable Interconnect Array (PIA) provides 100% routability. Other MAX architectural innovations, such as logic expanders, programmable register control terms, and decoupled register-I/O, guarantee maximum use of the chip's resources in any application. In addition, the MAX macrocell includes options such as asynchronous clocking, and Preset and Clear logic inputs for all registers to directly implement TTL functions. For additional information, refer to Application Note 17 (Integrating an Intelligent I/O Subsystem).

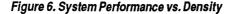

## What system level performance can be expected from MAX devices?

Logic clock rates quoted for MAX devices are actual worst-case clock frequencies obtained for basic logic building blocks (such as counters, shift registers, etc.) integrated into the chip. Unlike  $f_{MAX}$  flip-flop toggle frequencies, which are commonly quoted for other technologies and have no direct correlation to true system performance, practical logic blocks can be built that operate at these clock rates. Performance of MAX devices,

1

even in extremely complex configurations, is compatible with today's 25-MHz or faster processors. See Figure 6.

For example, basic building block functions that do not require logic expanders can run at 76 MHz in an EPM5032. A complex state machine implemented in the EPM5032 and using logic expanders, runs easily at 47 MHz. An EPM5016 delivers 15-ns combinatorial logic for fast decoders and muxes.

### ◆ Will extended-temperature range MAX devices be available?

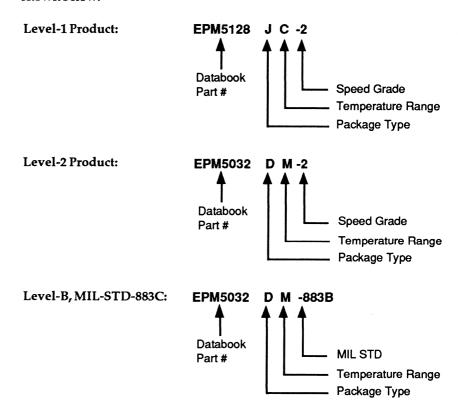

Altera offers its EPLDs in a choice of device operating temperature ranges: Commercial (0° C to +70° C), Industrial (-40° C to +85° C) and Military (-55° C to +125° C). MAX devices will be offered in similar grades. In addition, MAX devices will be available fully screened to the requirements of Mil Standard 883B, Level C.

### What are our packaging options with EPLDs?

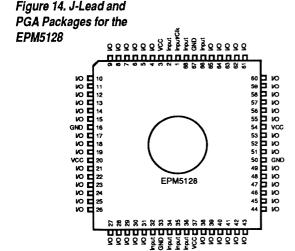

MAX EPLDs are currently available in a variety of I/O counts and package styles from 20 to 100 pins. UV-erasable, reprogrammable ceramic windowed parts are available in dual-in-line (DIP), pin-grid-array, and J-lead chip carrier packages. Small-Outline (S.O.) and quad-flat-pack (QFP) device options are also under development. Plastic one-time-programmable (OTP) devices will be offered in DIP and surface-mount package styles for lowest production costs. As a result, whether a customer's board technology is through-hole or surface-mount, MAX EPLDs fit.

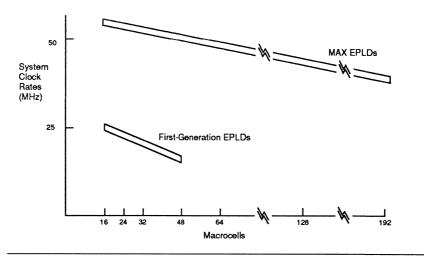

### ♦ How much does MAX cost relative to other approaches?

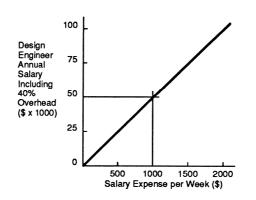

"...getting to market six months earlier can triple the profits of a product..." Studies by Integrated Circuit Engineering, an independent semiconductor market research firm, indicate that for system volumes below 10,000 units per code, programmable logic devices are the most cost-effective technology—less costly than TTL, less costly than gate arrays, less costly than any other logic technology. See Figure 7.

Figure 7. PLD Cost-Effectiveness

Also, based on a study by McKinsey and Company, a market research firm, getting to market six months earlier can triple the profits of a product over its life (see Figure 8). So the user-configurable approach of MAX, which allows a designer to get his design into his system the same day, provides the lowest overall cost and highest profit approach for small- to medium-volume systems.

Sales Volume

Second to Market

Second to Market

1 2 3 4 5

## ♦ What are the benefits of MAX EPLDs versus RAM-based programmable gate arrays?

Some of the benefits of MAX technology, when compared to RAM-based programmable gate arrays, are:

- ☐ Easy-to-understand logic-array architecture—Unlike exotic programmable gate array architectures, MAX uses logic-array structures familiar to PLD/TTL system designers.

- ☐ Stand-alone chips that require no support devices—RAM-based programmable gate arrays typically require additional external memory chips and waste device pins for initialization.

- Non-volatile technology—MAX's non-volatile CMOS EPROM technology means that MAX EPLDs can be used reliably in critical portions of system designs. They do not require initialization during power-up and do not lose their logic configuration in the event of power supply "brown-out."

- ☐ Efficient implementation of combinatorial and registered functions—Unlike programmable gate arrays that implement arithmetic and combinatorial logic poorly, the MAX architecture supports both types of logic efficiently. This ability translates into two to three times the performance in real applications.

- ☐ A range of device sizes for all design problems—MAX chips will range from fast 20-pin devices (standard PAL complexity) to 100-lead chips, with up to 384 registers and latches. Programmable gate arrays, on the other hand, provide no support for small to medium logic blocks common in today's system design.

- ☐ Programmable Interconnect Array (PIA) for guaranteed routability— Unlike programmable gate arrays with limited signal routing channels (as illustrated in Figure 9), MAX's PIA is programmed by the MAX+PLUS software to route designs without manual intervention. And MAX+PLUS automatically compiles complex logic designs in minutes, unlike programmable gate arrays that can take hours or days.

- ☐ State-of-the-art design tools—Programmable gate array software is universally known to be hard to use, requiring a long training process and designer "hand-holding" during compilation, and operating at a very low level. MAX+PLUS software (shown in Figure 10) speaks the designer's language—with Boolean equation, state machine, and TTL schematic design methods—and requires minimal knowledge of the inner workings of MAX. Manual routing of the design is never required.

So MAX is easier to use, gives higher real performance, and more effective logic utilization than programmable gate arrays.

## Figure 9. Routing Schemes

#### Gate Array LCA

Conventional Channel Routing

Delay

MAX

Programmable Array

### ♦ How reliable is MAX EPLD technology?

MAX EPLD technology is based on EPROM memory technology, which has proven highly reliable over the past 15 years. While the application of this technology to programmable logic is relatively new, the underlying principles and reliability are well demonstrated. Millions of EPROM memory components have been shipped and used in systems for years, demonstrating their reliability. Millions of CMOS EPLDs have similarly been shipped over the past five years with the same positive results.

### ◆ Are there any second sources for MAX?

Cypress Semiconductor, a leading manufacturer of high-performance CMOS ICs, second-sources the MAX product family, guaranteeing continuity and variety of supply to MAX users.

## ♦ Why does Altera provide its own design tools instead of relying on third-party logic compilers?

Providing leading-edge IC technology is not enough. Design tools must be able to exploit the capabilities of the silicon to maximize designer productivity. By way of analogy, it is possible to drive a wood screw into a block of wood with a hammer, but a screwdriver does a faster job and results in a stronger bond. The screwdriver and screw are complementary and give the optimum result. Similarly, general-purpose design tools frequently cannot use new device features effectively. Altera's MAX+PLUS design system supplies all the capability customers have come to expect in a state-of-the-art CAE system, and supports all features of the MAX family fully (see Figures 11 and 12). For example, Altera's MAX+PLUS system provides the following advantages:

"...it is possible to drive a wood screw into a block of wood with a hammer..."

- ☐ Hierarchical schematic capture—Supports a structured approach to large design management.

- ☐ Altera Hardware Description Language (AHDL) entry—Supports hierarchical behavioral logic descriptions using group, conditional, arithmetic, and relational operators.

- ☐ **User-defined macro libraries**—Allow the standardization of frequently used custom functions within a project.

- ☐ **Timing simulation**—Models actual chip response with 100-picosecond resolution.

- ☐ Advanced logic minimization and synthesis—Maps TTL designs onto MAX architecture for maximum efficiency/compilation ease.

- ☐ Interactive delay prediction—Provides quick point-to-point delay prediction in the logic design based on actual device timing parameters.

- ☐ Automatic error location—By closely linking the MAX logic compiler and language and graphic front ends, design entry errors are reported quickly to minimize debug time.

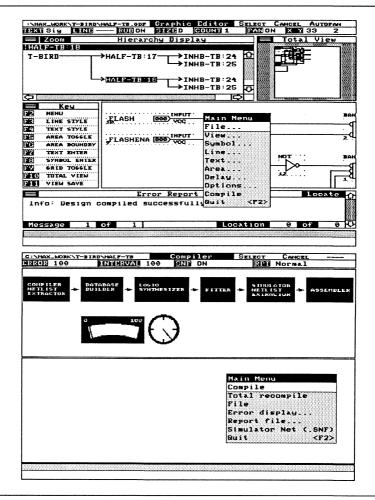

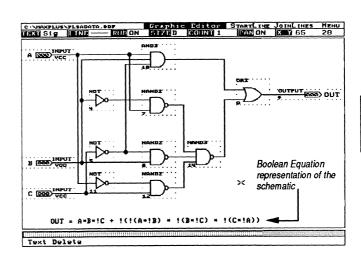

### Figure 11. MAX+PLUS Graphic Editor Screen

The hierarchical Graphic Editor provides a multiwindowed, menu-driven environment.

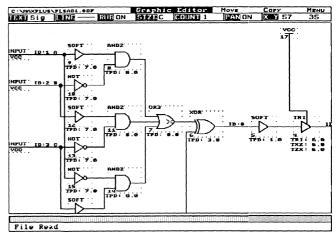

### Figure 12. MAX+PLUS Compiler Screen

The Compiler uses minimization, logic synthesis, and heuristic fitting algorithms to place designs into MAX EPLDs.

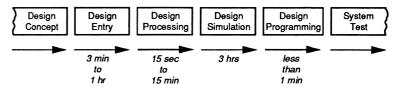

### ♦ How long does it take to learn the MAX+PLUS tools? How quickly can a typical design be implemented?

The learning curve for Altera's tools, as with any system, is a function of the designer's previous CAE tool experience. For a user familiar with a PC and A+PLUS, MAX+PLUS designs can be generated by the end of the first day. For the inexperienced PC user, a typical learning curve might stretch to a week. MAX+PLUS software has been structured to minimize surprises and automate all design compilation steps once the design is entered. Figures 13 and 14 illustrate the typical design cycle and cost savings.

"...6 hours after receiving MAX+PLUS, the manager had entered and successfully fit his design into an EPM5128."

Figure 13. EPLD Design Methodology

This ease of use is in stark contrast to the difficulties typically encountered in using more primitive programmable logic design tools. Point-by-point comparisons have shown that the MAX approach is easier to learn and use than alternatives such as programmable gate arrays. In one instance, a design manager assigned a programmable gate array design to a junior engineer. The design was targeted for a device specified as a 9000-gate programmable gate array, but in theory would use only 60% of the device's resources. After three months, the design was still not implemented due to routing problems. The manager took over the project himself, and was unsuccessful in improving matters after a week of constant effort. The programmable gate arrays's inherent architectural weakness had limited its gate utilization to only 30%. At this juncture, the manager turned to the

Figure 14. CAE Investment Saves Time & Money

Altera approach: six hours after receiving MAX+PLUS software, the manager had entered and successfully fit his design into an EPM5128. Quite a contrast to three man-months of wasted effort.

As an added support feature, the Altera Applications Hot Line is available to answer any device or tool questions in real-time over the telephone.

1

Moreover, the Electronic Bulletin Board Service, accessible via modem, keeps Altera users up-to-date on new EPLD applications tips and news.

### ♦ Why does Altera charge for its design tools?

Providing timely support of new device architectures such as MAX takes considerable investment on Altera's part. Fully 50% of Altera's development efforts are in new design tools as opposed to ICs. To develop and maintain these productivity-enhancing tools, Altera must charge a fair price. Second-sourcing of Altera components also means that Altera cannot always recoup its tool development investment from component sales and must directly charge for them. Placed in perspective, the expense of a design engineer's salary and overhead can easily amount to \$100,000 or more per year. An investment of just under \$5,000 in MAX+PLUS CAE tools can save weeks of engineering effort, and pays for itself on the first project!

"...an investment of just under \$5000 in MAX+PLUS CAE tools can save weeks of engineering effort..."

## ◆ Does the MAX+PLUS design system obsolete previous EPLD design tools (e.g., A+PLUS) and require a new learning curve?

No. As shown in Figure 15, the MAX+PLUS design system offers a superset of the capability found in A+PLUS. Most A+PLUS users are up to speed on MAX+PLUS in a day, entering schematics and compiling designs. The pop-up menu/mouse-driven interface is easy to use. New features such as simulation and waveform editing are intuitive and easy to learn.

A+PLUS is still recommended for the EP-series (EP610, EP910, etc.) of zero-power EPLD devices, which draw microamps of supply current at low input frequencies, and are ideal for power-sensitive applications such as hand-held instrument and telecommunications. So the EP- series is an excellent complement to the EPM-series, where power is the issue. For convenience, MAX+PLUS accepts EP-series designs generated with A+PLUS, expanding the designer's options with minimal effort.

Altera Corporation Page 19

# ◆ How do we integrate Altera design tools into our workstation strategy using Mentor, Valid, VIEWlogic, Orcad, or other system-level design tools?

Altera's design tools support industry-standard EDIF netlist generation, while EDIF netlist input is under development. Leading workstation vendors and third-party tool vendors have committed to support EDIF as well, allowing efficient tool linkage. In addition, third-party vendors such as Logic Automation Inc. have developed interfaces, device models, and other products that allow Altera EPLDs to be integrated into system-level design tools. Altera will encourage similar support, so that the designer can harness the horsepower of MAX+PLUS logic synthesis with existing design entry and verification tools.

#### ♦ How do we generate test vectors for MAX EPLDs?

Special-purpose test vectors are not necessary to ensure the functionality or quality of programmed EPLDs. EPLDs are generically tested, which means that every programmable connection is checked at the factory. All possible faults are pre-tested as part of the standard manufacturing and test flow—a major benefit of erasable programmable technology. As a result, Altera guarantees 100% programming yield of its components on approved programming equipment, unlike fuse-based programmable components in which programmable connections cannot be pre-tested.

To summarize testability criteria:

EPLDs are generically testable.

- All EPLDs are 100% tested at factory for functionality, programmability, and performance.

- ☐ Altera guarantees 100% programmability on certified programmers, thus yielding lower cost and high reliability.

- ☐ Plastic one-time-programmable (OTP) EPLDs incorporate special test modes to ensure same programming yield as reprogrammable/windowed parts.

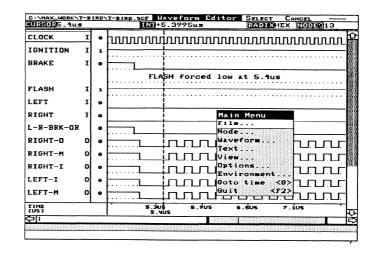

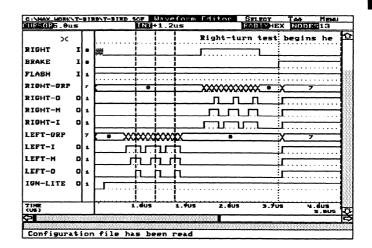

If test vectors are required for system documentation or other purposes, the MAX+PLUS Simulator, a timing simulator, can provide an effective means to predict device response to input vector sequences (see Figure 16). The MAX+PLUS Simulator's output file can be translated to the appropriate tester input format by tester-specific conversion routines.

## Figure 16. MAX+PLUS Waveform Editor Screen

The Waveform Editor allows entry and modification of input stimuli and comparison of simulation waveforms.

### ◆ Can we convert our MAX designs to gate arrays?

For very high volume designs, or for designs that are stable over a period of years, a gate array might still be an appropriate successor to a MAX design. MAX+PLUS EDIF output can support design transfer at a detailed gate level. In addition, since MAX+PLUS supports TTL schematic entry, higher-level macrofunction translation is very straightforward. No complex format conversions are necessary. MAX schematics can be entered into the target design system of an ASIC vendor, typically in a matter of days. Since the MAX architecture supports features commonly found in TTL functions directly (asynchronous preset and clear, complex clock functions, edge-triggered or flow-through flip-flops, etc.), no functional translation is necessary during the entry process.

### **Summary**

The MAX family of high-density, high-performance EPLDs has been developed by Altera as a complete set of user-configurable logic building blocks for a wide range of system applications. Through the easy-to-learn, easy-to-use MAX+PLUS set of logic design tools, designers can exploit the maximum capabilities of the programmable MAX chips in minimum time. It is this combination of logic density, speed, and designer productivity that will make MAX the industry-standard logic family of the 1990s.

|           | Contents                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Section 1 | MAX Family Overview                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |

|           | MAX EPLD Family Architecture                                                                                                                                                                                                                                                                                                                                                                                             |                                        |

| Section 2 | Data Sheets                                                                                                                                                                                                                                                                                                                                                                                                              |                                        |

|           | MAX Family: Device & Software Overview                                                                                                                                                                                                                                                                                                                                                                                   | 33<br>53<br>83<br>85<br>97             |

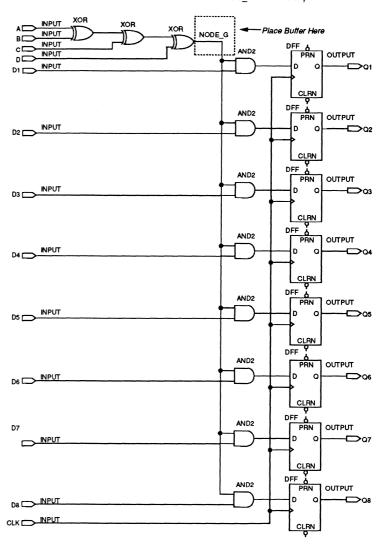

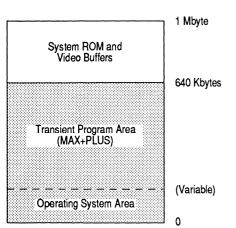

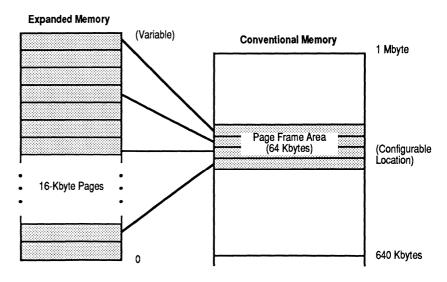

| Section 3 | Application Notes and Briefs  Integrating PAL and PLA Devices with the EPM5032 Integrating an Intelligent I/O Subsystem with a Single EPM5128 Understanding MAX EPLD Timing Using Expanders to Build Registered Logic in MAX EPLDs Design Guidelines for MAX EPLDs Optimizing Memory for MAX+PLUS Simulating Internal Nodes Choosing the Right EPLD for a State Machine Application Troubleshooting Programming Problems | 123<br>141<br>153<br>159<br>167<br>173 |

| Section 4 | General Information  Electronic Bulletin Board Service Ordering Information Package Outlines Applications Literature Altera Sales Offices Altera Sales Representatives and Distributors                                                                                                                                                                                                                                  | 199<br>201<br>202                      |

# MAX Family Device and Software Overview

January 1990

Data Sheet

# Product Summary

- ☐ Complete CMOS EPLD family providing a consistent design solution across a broad range of speed and density requirements

- MAX architecture providing the speed, ease of use, and familiarity of PAL devices with the density of programmable gate arrays

- $\Box$  15-ns combinatorial delays ( $t_{PD}$ ), counters as fast as 100 MHz, and pipelined data rates of 100 MHz

- ☐ High-density devices integrating up to 384 flip-flops and latches

- Package options from 20-pin DIPs to 100-pin Quad Flat Packs, in windowed, erasable, or one-time-programmable plastic

- ☐ Easy conversion to custom-masked devices for very high-volume production

- ☐ MAX+PLUS PC-based design tools able to compile large designs in minutes

- ☐ EDIF industry-standard workstation and third-party interfaces

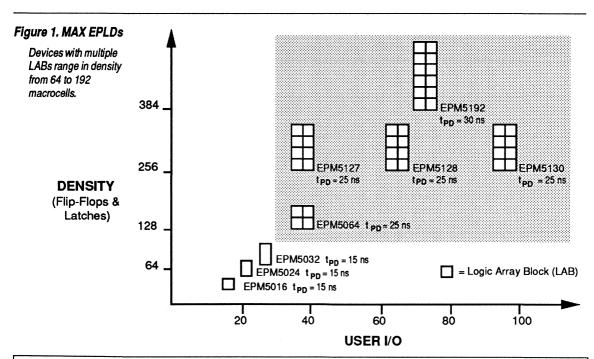

Figure 1 shows a graphical representation of device density and the number of I/O pins, as well as the number of Logic Array Blocks (LABs) per device.

# Family Highlights

#### Multiple Array MatriX (MAX) architecture solves speed, density, and design flexibility problems

- Advanced macrocell array provides registered, combinatorial, or flow-through latch operation.

- Expander product term array automatically provides additional combinatorial or registered logic.

- Decoupled I/O block with dual feedback on I/O pins allows flexible pin utilization.

- Programmable Interconnect Array provides automatic 100% routing in devices with multiple LABs.

- Each macrocell supports synchronous or asynchronous operation by every macrocell, using single or multiple clocks per device.

#### **♦** MAX Device Performance

- Pipelined data rates to 100 MHz

- Counters as fast as 100 MHz

- t<sub>pp</sub> performance from 15 ns to 30 ns

- Advanced 0.8 micron CMOS EPROM technology

#### **♦** MAX Device Logic Density

- 16 to 192 macrocell devices

- 20- to 100-pin packages

- 32 to 384 flip-flops and latches

- More than 32 product terms on a single macrocell

- Product term expansion on any data or control path

#### ♦ MAX+PLUS Design Tools

- Design entry via unified, hierarchical schematic capture and Altera Hardware Description Language (AHDL)

- Fast, automatic design processing with logic synthesis

- Automatic device fitting, no hand editing needed

- Hardware and software design verification tools

- Compiles a 16-bit counter in 34 seconds on a 16-MHz 386 personal computer

- ◆ EDIF reader and writer interfaces to MAX+PLUS provide convenient paths to Dazix, Mentor, Valid, and other workstations.

### Overview

The Altera Multiple Array MatriX (MAX) family of EPLDs provides a user-configurable, high-density solution to general-purpose logic integration requirements. The innovative architecture and state-of-the-art process used by the MAX EPLDs offer LSI density, without sacrificing speed.

MAX architecture can replace large amounts of 7400-series SSI and MSI TTL and CMOS logic. For example, a 74161 counter utilizes only 3% of the 128 macrocells available in the EPM5128. Similarly, a 74151 8-to-1 multiplexer consumes less than 1% of the more than 1,000 product terms available in the EPM5128. Thus, the designer can replace 50 or more TTL packages with just one MAX EPLD. The MAX family is available in a range of densities and packages, shown in Figure 1. By standardizing with a few MAX building blocks, the designer can replace hundreds of different 7400-series and PLD part numbers currently used in most digital systems while gaining the flexibility of a programmable, re-usable technology.

The family is based on an architecture of flexible macrocells grouped into Logic Array Blocks (LABs). Additional product terms, called expander product terms (expanders), are within each LAB. Expanders are used and shared by the macrocells to allow complex functions (more than 32 product terms) to be easily implemented in a single macrocell. A Programmable Interconnect Array (PIA) globally routes all signals in devices with more than one LAB. MAX architecture is fabricated with an advanced 0.8-micron CMOS EPROM process that yields devices with three times the integration density and twice the system clock speed of the other programmable solutions.

All MAX family members use an identical architecture, except for the PIA. Larger devices (EPM5064, EPM5127, EPM5128, EPM5130, and EPM5192) add the PIA to provide high performance and 100% routability for larger single-chip design tasks. This division between PIA and non-PIA MAX devices provides extremely fast parts for small to medium logic design tasks, while continuing to provide high performance when the logic design task grows to hundreds of TTL chip equivalents.

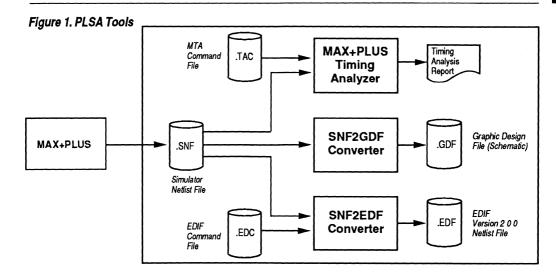

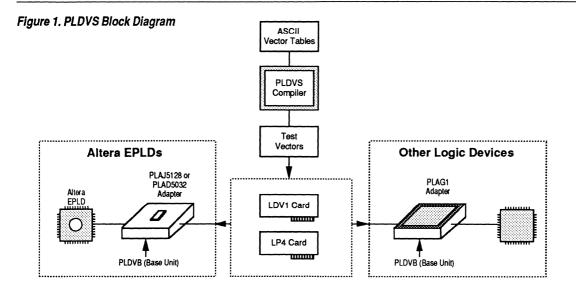

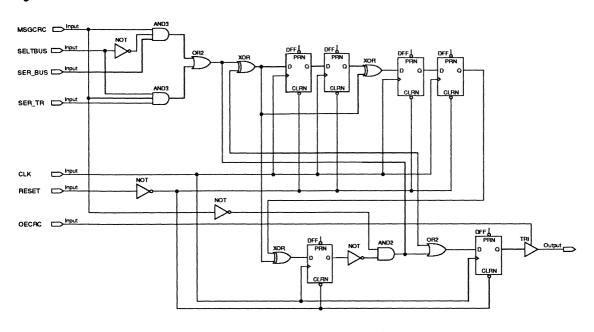

The density and flexibility of the MAX family is complemented by the MAX+PLUS Development System. MAX+PLUS is a PC-based design system that is optimized specifically for MAX architecture. Hierarchical schematic entry is used to capture the design. State machine, truth table and Boolean equation entry mechanisms are also supported with the Altera Hardware Description Language (AHDL). Design methods may be mixed within a design's hierarchy, using the entry method most appropriate for the task. An integrated timing simulator provides full AC simulation and an interactive Waveform Editor which speeds waveform creation and debugging. Optional hardware and software verification tools include the Programmable Logic Synthesis Analyzer (PLSA) Tools for synthesis analysis and transfer to workstation-based board-level simulators, and the Altera Personal Logic Design Verification System (PLDVS) for hardware function test and continuity check programming. See the appropriate software data sheets for additional information.

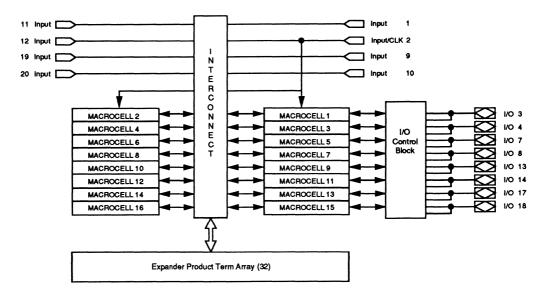

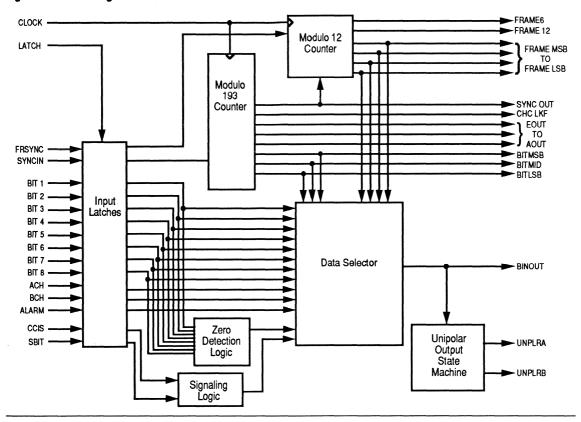

## MAX Device Architecture

The architecture for MAX devices consists of five major elements: the Logic Array Block (LAB), the MAX macrocell, expander product terms, the I/O control block, and the Programmable Interconnect Array (PIA). A description of each follows.

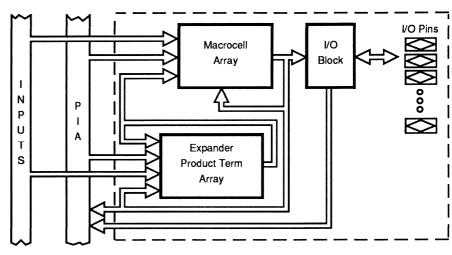

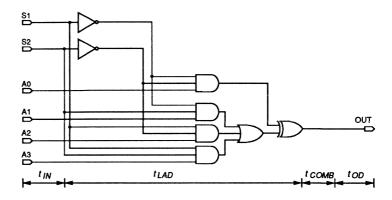

## **Logic Array Block**

The Logic Array Block, shown in Figure 2, is the heart of MAX architecture. It consists of a macrocell array, an expander product term array, and an I/O control block. The number of macrocells, expanders, and I/O varies, depending on the device used. Global feedback of all signals is provided in the LAB, giving each functional block complete access to the LAB's

Figure 2. LAB Block Diagram

resources. The LAB is fed by a dedicated input bus (PIA), which is used to interconnect devices that contain more than one LAB. The PIA provides sufficient interconnections to fully use all macrocells within a device without routing constraints. Macrocell and I/O pin feedbacks enter the PIA, so that other LABs in the device have access to them. MAX EPLDs that have a single LAB use a global interconnect network, and have no need for a PIA.

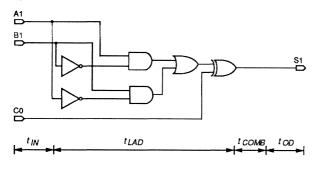

### **MAX Macrocell**

Traditionally, PLDs have been divided into PLA (programmable-AND/programmable-OR), and PAL (programmable-AND/fixed-OR) architectures. PAL architecture provides faster input-to-output delays, but can be inefficient due to the fixed product-term distribution. Statistical analysis of PLD logic designs has shown that 70% of all logic functions require at most three product terms. The remaining 30% need anywhere from 4 product terms to as many as 30 in some complex combinatorial or state machine designs.

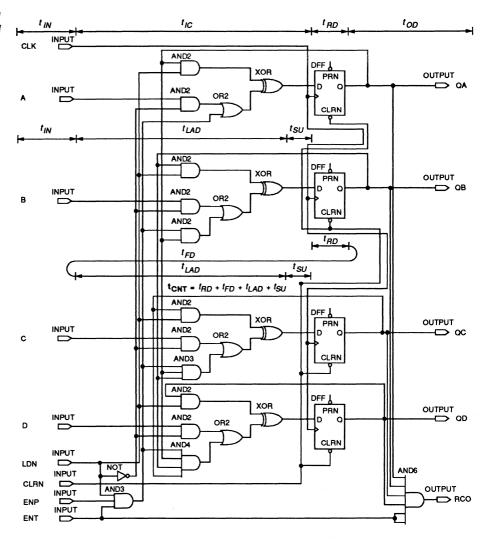

The macrocell structure of MAX is based on three product terms that are able to add additional product terms when necessary. Each macrocell consists of a product term array and a configurable register (see Figure 3). Combinatorial logic is implemented with three product terms ORed together, feeding an XOR gate. The second input to the XOR gate is also controlled by a product term, providing the ability to control active-high or active-low logic. MAX+PLUS software uses the XOR gate to implement complex mutually exclusive-OR arithmetic logic functions, or to perform DeMorgan's Inversion, reducing the number of product terms required to implement a function.

Figure 3. Macrocell Block Diagram

If more product terms are required to implement a given function, they may be added to the macrocell from the expander product term array. These additional product terms may be added to any macrocell to allow the designer to build gate-intensive logic, such as address decoders, adders, comparators, and complex state machines, without using extra macrocells.

Logic is automatically allocated by the MAX+PLUS Compiler during compilation. Alternatively, the designer can choose specific logic assignments for macrocells and expanders.

The register in a MAX macrocell may be programmed for D, T, JK, or SR operation; it may also be configured as a flow-through latch for minimum input-to-output delays. The register may be by-passed entirely for purely combinatorial functions. In addition, each register supports asynchronous Preset and Clear, allowing asynchronous loading of counters or shift registers, as found in many standard TTL functions. These registers may be clocked with a synchronous system clock or an asynchronous clock from the logic array.

### **Expander Product Terms**

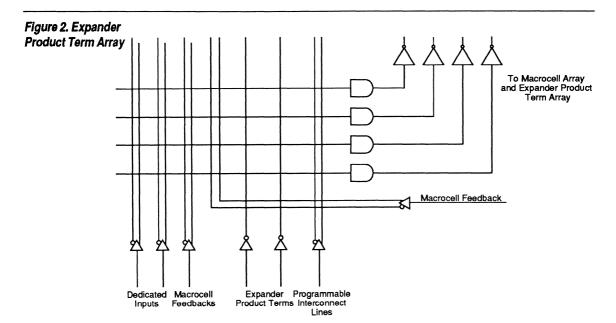

Expander product terms are fed by the dedicated input bus, PIA, macrocell feedback, I/O pin feedback, and other expanders (see Figure 4). Expander outputs can connect to every product term in the macrocell array, allowing expanders to be "shared" by the product terms in the Logic Array Block. One expander may feed all macrocells in the LAB or multiple product terms in the same macrocell. Since these expanders feed the secondary product terms (Preset, Clear, Clock, and Output Enable) of each macrocell, complex logic functions may be implemented without using another macrocell. Likewise, expanders may feed and be shared by other expanders to implement complex multi-level logic and latches. Expanders are normally allocated in parallel to ensure highest performance.

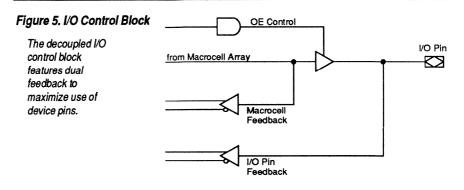

### I/O Control Block

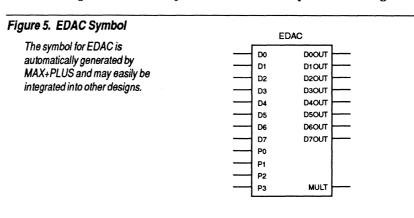

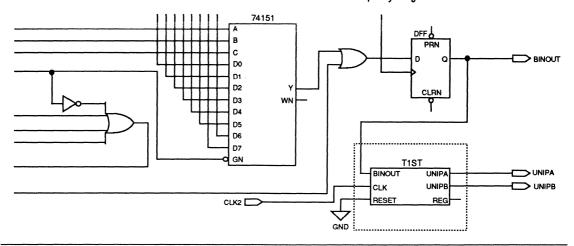

In the LAB, the I/O control block (Figure 5) is decoupled from the macrocell array. The tri-state buffer, controlled by a product term, drives the I/O pad. The input of the tri-state buffer comes from a macrocell in the associated LAB. The feedback path from the I/O pin may feed other blocks within the LAB, as well as the PIA.

Decoupling the I/O pins from the flip-flops allows buried registers in the LAB. At the same time, the I/O pin can be preserved as a dedicated input. The I/O pins may be used as dedicated outputs, bidirectional pins, or

Figure 5. I/O Control Block

additional dedicated inputs. Thus, applications requiring many buried flip-flops (such as counters, shift registers, and state machines) no longer consume both the macrocell register and the associated I/O pin, as they did in earlier devices.

### **Programmable Interconnect Array**

A major problem that has limited PLD density and speed has been signal routing, i.e., getting signals from one macrocell to another. A single array is used for small devices, and all signals are available to all macrocells. As devices increase in density, however, the number of signals being routed becomes very large, increasing the amount of silicon used for interconnections. The added loading on the internal connection path reduces the overall speed performance of the device. Larger MAX devices solve this problem since they are based on small, flexible LABs, connected by a PIA.

The PIA solves interconnect limitations by routing only the signals needed by each LAB. Every signal on the chip is in the PIA, which is programmed to give each LAB access only to the signals that it requires. This process solves any routing problems that may arise in a design, without degrading the performance of the device. Unlike masked or programmable gate arrays, which induce variable delays dependent on routing, the PIA has a fixed delay between any two LABs. The fixed delay eliminates undesired skews among logic signals that may cause glitches in internal or external logic.

# MAX+PLUS Development System

The MAX+PLUS Development System (Figure 6) is a complete, integrated CAE system optimized for MAX devices. MAX+PLUS is an open system interfacing a variety of tools, including many third-party tools. In addition, it supports all three phases of a design cycle: design entry, design compilation, and design verification.

Figure 6. PC-Based Design System

## **Design Entry**

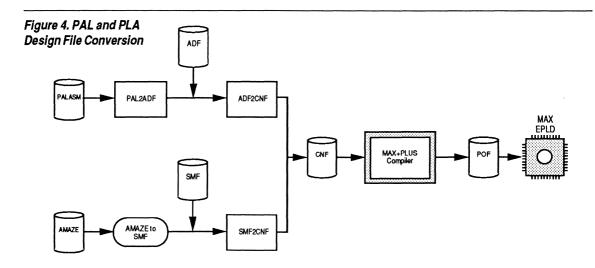

MAX+PLUS supports hierarchical graphic (schematic) and text design entry methods. In addition, designs created with other CAE tools may be placed in MAX EPLDs. MAX+PLUS accepts Altera Design File (ADF) netlists developed for EP-series devices, converts them into a format that can be read by the MAX+PLUS Compiler, and creates a symbol representing the design. Multiple ADFs may be connected in MAX+PLUS. The following companies and software packages produce ADFs: Altera (A+PLUS), Texas Instruments (A+PLUS), Intel (iPLDSI and iPLDSII), ViewLogic (Workview), and OrCAD (SDT III). Altera provides free utilities to enter EPLD designs with FutureNet and P-CAD, and convert their proprietary netlists into Altera ADF files. Free utilities to convert most PAL JEDEC files are also available from Altera Applications.

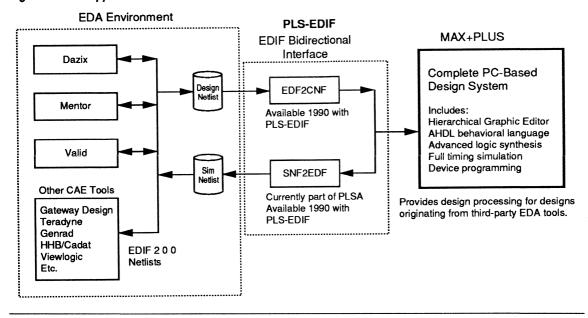

Altera offers a bidirectional EDIF interface (called PLS-EDIF) for companies that use workstations for design entry and board-level simulation. Users may transfer design information to the MAX+PLUS system with industry-standard EDIF 2 0 0 netlists (see Figure 7). Dazix, Mentor Graphics, and Valid Logic Systems provide EDIF netlists of schematic designs. These EDIF netlist descriptions may be translated into a format that can be

Figure 7. EDA Support

synthesized by the MAX+PLUS Compiler. PLS-EDIF is user-extendable and supports many libraries within the CAE vendors' schematic capture packages.

## Design Compilation

Once the design is entered, the design is compiled. The MAX+PLUS Compiler provides automatic processing of the design. The design is reduced to primitive, gate-level functions and any unconnected logic is automatically eliminated. Next, the design is minimized to reduce the logic equations to their most compact form. Logic synthesis then analyzes the minimized equations and applies sophisticated heuristic algorithms to the design to ensure maximum device utilization. Once the design has been synthesized, the Fitter does the actual logic placement within the chosen device. This fitting is the equivalent of gate array place and route, except it is performed automatically in MAX+PLUS. All design processing in MAX+PLUS is automatic, allowing the designer to concentrate on the logic design, not the mechanics of mapping it into the logic device.

## Design Verification

MAX+PLUS provides a full timing simulator for MAX EPLD designs. For users requiring board-level simulation capabilities, Altera offers interfaces to today's most popular simulators. With the PLSA's SNF2EDF tool or the bidirectional PLS-EDIF product, the Altera representation of a completed design (contained in the MAX+PLUS Simulator Netlist File) may be translated to an EDIF 2 0 0 netlist. This EDIF netlist contains all logical and timing information for the completed design and may be read by many third-party board-level simulators, such as Dazix DLS, Valid VALIDsim, Teradyne LASAR, HHB CADAT, and Gateway Verilog-XL.

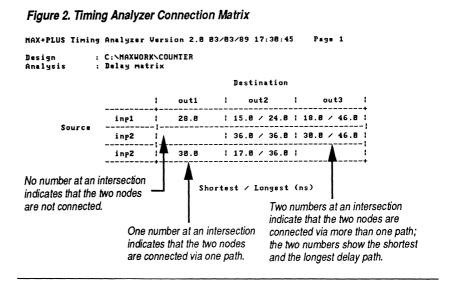

Altera offers tools to analyze and test MAX EPLD designs. The PLSA Tools' MAX+PLUS Timing Analyzer (MTA) provides user-configurable reports to help analyze critical delay paths, setup and hold timing, and overall system performance of any synthesized MAX EPLD design. The SNF2GDF tool creates a schematic representation of the synthesized design, including delay information. The representation shows exactly how the MAX+PLUS Compiler synthesized the design, whether the design was entered with a schematic, behavioral description, or third-party netlist.

The Personal Logic Design Verification System (PLDVS) product is a low-cost, general-purpose tester for functional verification of TTL or CMOS devices. It can be used for both production and engineering testing of gate arrays, and standard cell and programmable logic devices. Because PLDVS has a seamless interface with the MAX+PLUS Simulator, it is ideally suited for MAX EPLDs. The MAX+PLUS Waveform Editor may be used to define test vectors for Device Under Test (DUT) pins in PLDVS. Additionally, any simulation performed by the MAX+PLUS Simulator can be compared to actual device functionality by submitting the simulation to PLDVS. The Waveform Editor shows both the software simulation and the hardware functional test simultaneously, highlighting any discrepancy between them.

For more software information, refer to PLDS-MAX / PLS-MAX: MAX+PLUS Programmable Logic Development System, PLS-EDIF, and MAX+PLUS PLSA Tools. For more device information, refer to EPM5016 to EPM5032: MAX EPLDs with a Single LAB, EPM5064 to EPM5192: MAX EPLDs with Multiple LABs; and PLDVS: General Purpose PC-Based Tester.

Page 32 Altera Corporation

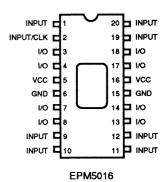

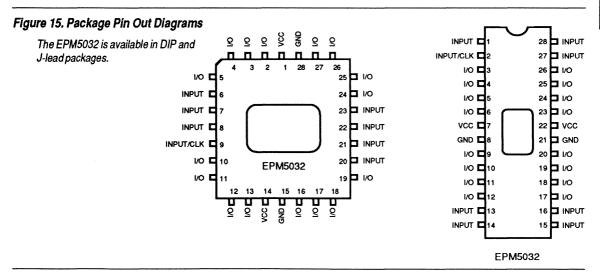

## EPM5016 to EPM5032 MAX EPLDs with a Single LAB

January 1990 Data Sheet

## Product Summary

- ☐ Single-LAB CMOS EPLDs offering a consistent design solution across a broad range of speed and density requirements

- □ 15-ns combinatorial delays (t<sub>PD</sub>), counters up to 100 MHz, and pipelined data rates of 100 MHz

- ☐ Fast, low pin-count devices for integration of up to 64 flip-flops and latches

- ☐ Package options from 20-pin dual-in-line packages (DIPs) to 28-pin J-lead packages, in windowed, erasable, or one-time-programmable plastic

- ☐ Dual feedback on all I/O pins

- Synchronous or asynchronous operation

- ☐ Single or multiple clocks

- ☐ MAX+PLUS PC-based design tools for compiling large designs in minutes

- ☐ EDIF industry-standard workstation and third-party interfaces

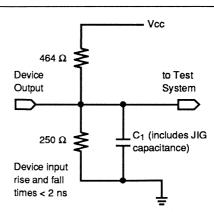

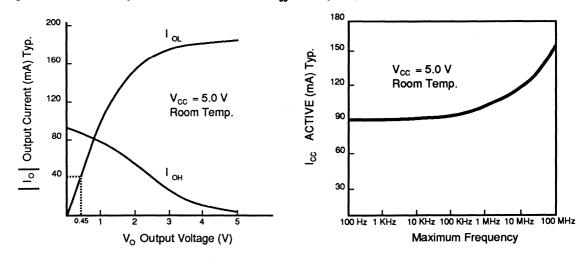

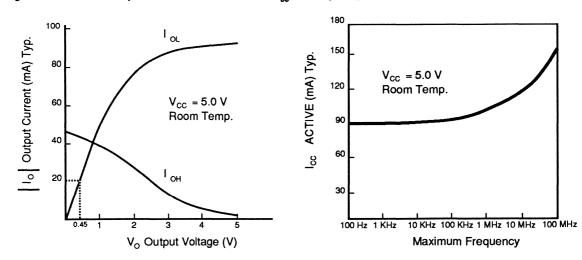

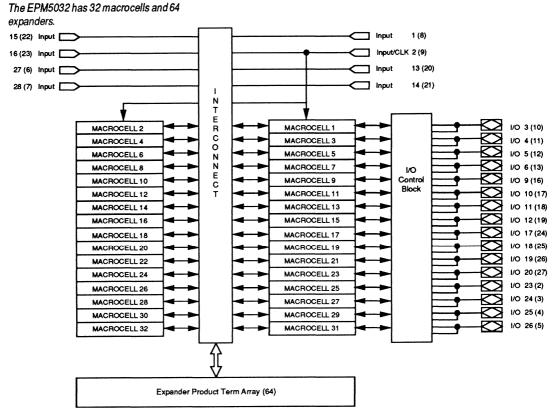

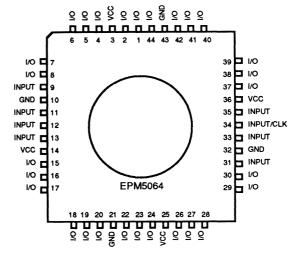

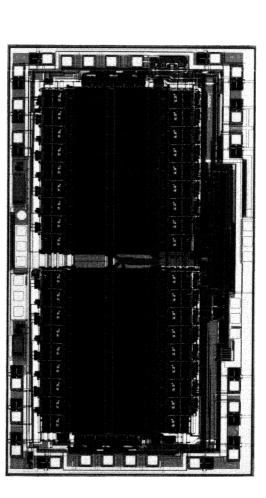

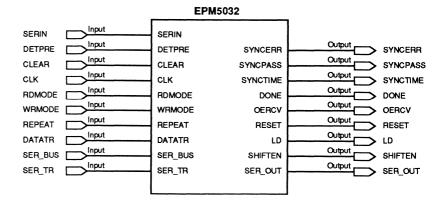

All EPLDs discussed in this Data Sheet are shown in Figure 1.

Figure 1. MAX Family Single LAB EPLDs

Surface mount packages are also available.

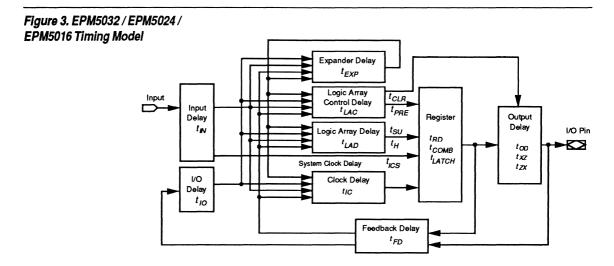

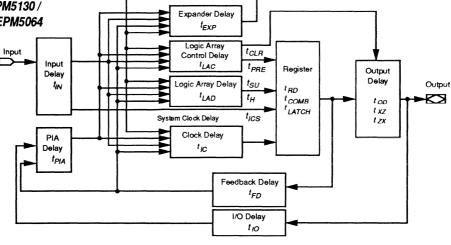

EPM5016